рефераты конспекты курсовые дипломные лекции шпоры

- Раздел Философия

- /

- Схемна реалізація логічних функцій на прикладі функцій “НЕ”, “І”, “АБО”, 3І–НЕ”, “3АБО–НЕ” та ін.

Реферат Курсовая Конспект

Схемна реалізація логічних функцій на прикладі функцій “НЕ”, “І”, “АБО”, 3І–НЕ”, “3АБО–НЕ” та ін.

Схемна реалізація логічних функцій на прикладі функцій “НЕ”, “І”, “АБО”, 3І–НЕ”, “3АБО–НЕ” та ін. - раздел Философия, Конспект лекцій з дисципліни Електротехніка, електроніка та мікропроцесорна техніка Розглянемо Схеми Деяких Логічних Елементів На Основі Іс, Що В...

Розглянемо схеми деяких логічних елементів на основі ІС, що виконують найпростіші логічні операції.

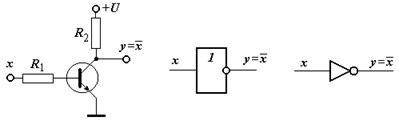

Рис. 1. Схема логічного елемента НЕ та її умовні позначення.

На рис. 1 представлені схема і умовні позначення інвертора, який реалізує логічну функцію НЕ (заперечення), тобто у= f(х) =  . При відсутності на вході цієї схеми сигналу на виході її буде висока напруга, відповідна рівню логічної 1, оскільки в цьому випадку транзистор закритий, і, отже, його внутрішній опір великий. При подачі на вхід схеми напруги, відповідної рівню логічної 1, на виході її буде низьке напруга, відповідна рівню логічного 0, оскільки в цьому випадку транзистор відкритий і опір його малий. Логіка роботи схеми описується таблицею істинності, в якій відображуються значення сигналів на вході і відповідні ним значення сигналів на виході схеми. Таблиця істинності схеми НЕ має вид табл. 1.

. При відсутності на вході цієї схеми сигналу на виході її буде висока напруга, відповідна рівню логічної 1, оскільки в цьому випадку транзистор закритий, і, отже, його внутрішній опір великий. При подачі на вхід схеми напруги, відповідної рівню логічної 1, на виході її буде низьке напруга, відповідна рівню логічного 0, оскільки в цьому випадку транзистор відкритий і опір його малий. Логіка роботи схеми описується таблицею істинності, в якій відображуються значення сигналів на вході і відповідні ним значення сигналів на виході схеми. Таблиця істинності схеми НЕ має вид табл. 1.

Таблиця 1. Таблиця істинності схеми НЕ.

| x | y |

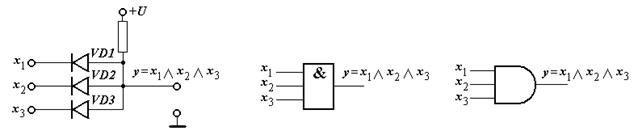

Приклад комбінаційної схеми, що реалізує функцію 3І (кон’юнкцію) тобто y = f(x 1, x 2 , x 3 ) = x 1 Ù x2 Ù x3 , і її умовні позначення наведений на рис. 2. Тут і далі перший символ в позначенні схеми – 3І визначає кількість входів схеми (наприклад, 3І – схема «І» із трьома входами).

Рис. 2.Схема логічного елемента 3І та її умовні позначення.

Операція кон’юнкції в цій схемі здійснюється за допомогою діодів. Якщо на входи x 1 ¸ x3 схеми подати напругу, що відповідає логічній 1, то діоди VD1÷VD3 будуть закриті, струм через них проходити не буде і на виході схеми буде висока напруга, яка відповідає логічній 1. Якщо хоча б на одному з входів цієї схеми буде низька напруга, яка відповідає логічному 0, то струм від джерела живлення +U пройде через відкритий діод і напруга на виході цієї схеми буде відповідати логічному 0. Таблиця істинності схеми І має вид табл. 2.

Таблиця 2. Таблиця істинності схеми 3І.

| x1 | x2 | x3 | y |

На рис. 3 наведена схема включення транзисторів в коло за схемою із спільним колектором. Це коло є повторювачем вхідного сигналу і застосовується в багатьох логічних схемах, здійснюючи операцію диз'юнкції вхідних сигналів (логічне додавання, операція АБО), тобто операцію y = f(x 1, x 2 , x 3 ) = x 1 Ú x2 Ú x3 . Наведені умовні позначення схеми 3АБО. Таблиця істинності цієї схеми має вид табл. 3.

Рис. 3. Схема логічного елемента 3АБО та її умовні позначення.

Таблиця 5. Таблиця істинності схеми 3АБО.

| x1 | x2 | x3 | y |

На рис. 4 наведена схема 3І–НЕ і її умовні графічні позначення. Схема реалізує функцію y = f(x) =  . Таблиця істинності схеми 3І–НЕ має вид табл. 4.

. Таблиця істинності схеми 3І–НЕ має вид табл. 4.

Рис. 4. Схема логічного елемента 3І–НЕ та її умовні позначення.

Таблиця 4. Таблиця істинності схеми 3І–НЕ.

| x1 | x2 | x3 | y |

На рис. 5 наведена схема 3АБО–НЕ і її умовні графічні позначення. Схема реалізує функцію y = f(x) =  . В цій схемі транзистори включені в коло за схемою із спільним емітером. Таблиця істинності схеми 3АБО–НЕ має вид табл. 5.

. В цій схемі транзистори включені в коло за схемою із спільним емітером. Таблиця істинності схеми 3АБО–НЕ має вид табл. 5.

Рис. 5. Схема логічного елемента 3АБО–НЕ та її умовні позначення.

Таблиця 5. Таблиця істинності схеми 3АБО–НЕ.

| х1 | х2 | х3 | y |

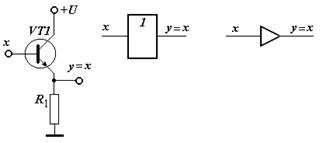

На рис. 6 наведена схема повторення і її умовні графічні позначення. Схема реалізує операцію повторення, тобто y = f(x) = х.

Рис. 6. Схема повторення і її умовне графічне позначення.

Таблиця 6. Таблиця істинності схеми повторення.

| x | y |

Наведені схеми логічних елементів є представниками так званих схем діодно–транзисторної логіки (ДТЛ). Транзисторно–транзисторні елементи (ТТЛ) з’явились як результат розвитку схем ДТЛ завдяки заміні діодів багатоемітерним транзистором (БЕТ) – інтегральним елементом, який об’єднує властивості діодних логічних схем і транзисторного підсилювача. Відміна БЕТ від транзисторів в тому, що він має кілька незалежних один від одного емітерів і один колектор.

Розглянемо роботу БЕТ на прикладі схеми 4І–НЕ (рис. 7) з простим інвертором (однополярним ключем).

а) б)

Рис. 7. Розподіл струмів в багатоемітерному транзисторі в схемі 4І–НЕ:

а) – на вхід подана напруга, що відповідає рівню логічної 1; б) – на вхід подана напруга, що відповідає рівню логічного 0.

Якщо на всі входи БЕТ подана напруга, що відповідає рівню 1 (Uвх1), емітери вхідного транзистора не отримають відкриваючого струму зміщення. При цьому струм, поданий в базу БЕТ через резистор R1, тече від джерела +U в коло колектора, зміщеного в прямому напрямку (рис. 7-а), і далі в базу транзистора VT2. Транзистор VT2 при цьому знаходиться в режимі насичення і напруга на виході схеми відповідає рівню логічного 0 (Uвих0).

Якщо на один з входів БЕТ подана напруга, що відповідає рівню 0 (Uвх0), перехід база–емітер БЕТ зміщується в прямому напрямку (рис. 7-б). Струм, поданий в його базу через резистор R1, потече в коло цього емітера. При цьому струм колектора БЕТ зменшується, транзистор VT2 вимикається і напруга на виході схеми стає рівною рівню логічної 1 (Uвих1).

З розвитком вдосконалення технології базовим для схем ТТЛ–типу став ключ із складним інвертором – двополюсний ключ (рис. 8-а). Використання складного інвертора в порівнянні з простою схемою дозволило збільшити швидкодію, завадостійкість, навантажувальну здатність і знизити вимоги до параметрів транзисторів.

Промисловість випускала кілька різновидів серій елементів ТТЛ–типу (серії стандартні 133, К155, швидкодіючі з діодами Шоттки 530, К531, мікропотужні з діодами Шоттки 533, К555).

а) б)

Рис. 8. Схеми чотирьохвхідних логічних елементів ТТЛ–типу:

а) – ключ із складним інвертором (схема І–НЕ); б) – розширювач АБО.

Майже всі логічні елементи, що входять до складу вказаних серій, можуть бути утворені комбінуванням двох базових схем: логічного елемента І–НЕ і розширювачів АБО на різне число входів (рис. 8).

Розширювач АБО разом з логічним елементом 4І–НЕ утворюють логічний елемент 4І–2АБО–НЕ (рис. 9).

Розширювач АБО разом з логічним елементом 4І–НЕ утворюють логічний елемент 4І–2АБО–НЕ (рис. 9).

Приєднуючи розширювач АБО (рис. 8-б) до точок 1, 2 (рис. 9) можна збільшувати число об’єднань по логічному входу АБО.

Для всіх схем ТТЛ–типу, що мають можливість розширення АБО, максимальне число об’єднань дорівнює 8.

До переваг ІС ТТЛ–типу можна віднести високий рівень схемно–технологічної відпрацьованості і, як наслідок, високий відсоток виходу придатних мікросхем і низьку їх вартість при виготовленні; хороші електричні параметри і характеристики, порівняно високу швидкодію при середній потужності споживання або середня швидкодія при малій потужності споживання; хороший чинник якості, тобто малий добуток часу затримки на потужність споживання; високу абсолютну та відносну завадостійкість; високі статичні і динамічні навантажувальні здатності; широкий функціональний набір елементів; зручність застосування (монтажу, компоновки, охолодження і т.д.), що забезпечує відносно прості інженерні методи конструювання на їх основі електронної апаратури.

Характеристики і параметри швидкодіючих ІС емітерно-зв’язаної логіки (ЕЗЛ) визначаються схемно–технічними, технологічними і конструктивними рішеннями елементів.

Розглянемо базовий логічний елемент ЕЗЛ–типу 2І/(2І–НЕ). Схема цього елементу складається з трьох кіл: струмового перемикача (СП), вихідних емітерних повторювачів (ЕП) і джерела опорних напруг (ДОН) (рис. 10).

Струмовий перемикач (СП), побудований на транзисторах VT1 ÷ VT3 і резисторах R1, R2, R6 ÷ R8, уявляє собою диференціальний підсилювач, що працює в ключовому режимі і має два або кілька входів. Він призначений для отримання першого ступеня логічної функції, підсилення вхідних сигналів за потужністю (в основному за струмом), формування парафазного (прямого та інверсного) вихідних сигналів та забезпечення необхідної завадозахищенності елемента.

Рис. 10. Логічний елемент 2І/2І–НЕ серії 500:

а) – схема елемента 2І/2І–НЕ; б) – умовне позначення елемента 2І/2І–НЕ.

Вихідні емітерні повторювачі (ЕП), що виконані на транзисторах VT5 та VT6, призначені для утворення другого ступеня логічної функції, підсилення вихідних сигналів за потужністю (за струмом), забезпечення заданої навантажувальної здатності при роботі на лінії зв’язку і зміщення рівнів сигналів за напругою для сумісності ІС за входом та виходом.

Джерело опорної напруги (ДОН), побудоване на транзисторі VT4, термокомпенсуючих діодах VD1, VD2 та резисторах R3 ÷ R5, призначене для забезпечення СП заданою опорною напругою, відносно якої здійснюється перемикання в ньому транзисторів.

Джерело опорної напруги забезпечує опорними напругами, як правило, кілька логічних елементів. В окремих випадках воно формує і інші опорні напруги, потрібні для схем ЕЗЛ–типу.

Базовий елемент ЕЗЛ–типу працює таким чином. Логічному 0 відповідає верхній рівень логічного сигналу (–0,9 В), логічній 1 – нижній рівень логічного сигналу (–1,7 В). Амплітуда логічного сигналу складає 0,8 В, опорна напруга дорівнює –1,3 В (середній рівень між верхнім і нижнім рівнем логічного сигналу).

При подачі на всі входи напруги –1,7 В транзистори VT1 і VT2 закриваються, транзистор VT3 відкривається (оскільки напруга на його базі вища за напругу на базах вхідних транзисторів) і крізь нього потече емітерний струм, що визначається резистором R6. Цей струм, зменшений на значення базового струму транзистора VT3, створює на його колекторному навантаженні падіння напруги, що дорівнює ~0,9 В. В інверсному плечі СП струму немає, і на колекторі транзисторів VT1 і VT2 встановлюється напруга, що дорівнює ~ –0,1В, за рахунок падіння напруги на резисторі R1 від базового струму транзистора VT6. Транзистори вихідних ЕП працюють весь час в активному режимі, і падіння напруги на їх емітерних переходах складає ~0,8 В. В результаті на прямому виході елемента встановлюється напруга, що відповідає логічній 1, тобто –1,7 В, а на інверсному – напруга, що відповідає логічному 0, тобто –0,9 В. Якщо ж хоч би на один вхід елемента подається напруга –0,9 В, відкривається інверсне і закривається пряме плече струмового перемикача СП і ситуація змінюється на протилежну.

До переваг ІС ЕЗЛ–типу можна віднести задовільну схемно–технологічну відпрацьованість і, як слідство, задовільний середній процент виходу придатних мікросхем і відносно невисоку їх вартість при виготовленні; високу швидкодію при середній потужності споживання або надвисоку швидкодію при великій потужності споживання; хороший фактор якості, тобто малий добуток часу затримки на потужність споживання; здатність працювати на низькоомні узгоджені лінії зв’язку і навантаження; хорошу відносну завадостійкість; високу стабільність динамічних параметрів при зміні температури і напруги живлення; високу навантажувальну здатність та ін. ІС ЕЗЛ–типу отримали достатньо широке розповсюдження при конструюванні швидкодіючої і високопродуктивної обчислювальної техніки. Головний недолік ІС ЕЗЛ–типу – висока потужність споживання, що спричиняє потребу в потужних блоках живлення, створювати системи інтенсивного охолодження.

Інтегральні схеми на МОП–транзисторах (метал–оксид–напівпровідник) мають нижчу швидкодію, ніж елементи ТТЛ- або ЕЗЛ–типу. Однак ці елементи відрізняються меншою потужністю споживання, більшою навантажувальною здатністю і завадостійкістю, потребують меншу площу на поверхні ІС, дешевше елементів ТТЛ- і ЕЗЛ–типу. Тому вони широко застосовуються, особливо в цифрових пристроях невисокої швидкодії або в пристроях, для яких важлива висока ступінь інтеграції.

В основі роботи МОП–транзисторів лежить ефект керування полем (польові транзистори). По принципу дії вони є аналогами електронних ламп, оскільки керуються напругою, а не струмом. МОП–транзистори бувають n- і p–типу.

На рис. 11-а наведена схема інвертора на МОП–тразисторі n–типу. Виток В транзистора виконує тут роль, схожу з роллю емітера в транзисторах. До затвору З (входу схеми) прикладається керуюча напруга, стік С є виходом схеми. При зміні напруги на затворі З змінюється опір між витоком В і стоком С (від сотень Ом до сотень мегаОм), що призводить до зміни струму, що протікає через транзистор, і вихідної напруги схеми. При надходженні на затвор З сигналу високої напруги, опір між витоком В і стоком С падає і на виході встановлюється низька напруга. При надходженні на вхід сигналу низького рівня опір транзистора стає дуже великим і на виході встановлюється висока напруга. Як навантажувальний опір в схемах на МОП–транзисторах технологічно зручно використовувати МОП–транзистор, на затвор З якого подається напруга, що ставить його в режим відкритого транзистора (рис. 11-б).

Поряд з навантажувальним резистором в схемах на МОП–транзисторах використовуються МОП–транзистори p–типу, живлення яких і керування проводиться від’ємними напругами. Інвертор з транзисторами n- і p–типів (доповнюючі (комплементарні) транзистори) наведений на рис. 11-в. Тут при надходженні на вхід високої напруги відкривається нижній транзистор, а верхній закривається, і, навпаки, при надходженні на вхід низької напруги відкривається верхній транзистор, а нижній закривається. Схеми з доповнюючими транзисторами (комплементарні схеми) відрізняються малою потужністю споживання і більш високою швидкодією, оскільки в колах заряду і розряду паразитних ємностей виявляються включеними малі опори відкритих транзисторів.

Рис. 11. Схема логічного елемента на МОП–транзисторах.

а) – з навантажувальним резистором, б) – з навантажувальним транзистором n–типу, в) – з навантажувальним транзистором p–типу.

Рис. 12. Комбінаційні МОП-схеми:

а) – елемент І–НЕ з навантажувальним транзистором; б) – елемент АБО–НЕ з навантажувальним транзистором; в) – елемент І–НЕ з доповнюючими транзисторами; г) – елемент АБО–НЕ з доповнюючими транзисторами.

Схеми, що реалізують функції І або АБО, будуються відповідно послідовним і паралельним включенням МОП–транзисторів. При цьому звичайно на виході схеми отримуються функції І – НЕ або АБО – НЕ.

Принцип роботи логічних елементів на МОП–транзисторах можна зрозуміти із схем, наведених на рис. 12. Групи логічних схем із спільними технічними характеристиками об’єднуються в серії.

Серія – комплект інтегральних схем, що мають єдине схемне і конструктивно–технологічне виконання. До складу цифрових серій поряд з комбінаційними схемами, що виконують прості логічні функції, і тригерними схемами (елементи пам’яті) входять також схеми, що уявляють собою цілі вузли і блоки арифметичних пристроїв.

Основні електричні параметри логічних схем – спільні для всіх серій цифрових інтегральних схем, що дозволяє порівнювати їх між собою: швидкодія, потужність споживання, завадостійкість, коефіцієнт розгалуження виходу (навантажувальна здатність), коефіцієнт об’єднання на вході.

– Конец работы –

Эта тема принадлежит разделу:

Конспект лекцій з дисципліни Електротехніка, електроніка та мікропроцесорна техніка

ХЕРСОНСЬКИЙ НАЦІОНАЛЬНИЙ ТЕХНІЧНИЙ УНІВЕРСИТЕТ... Кафедра енергетики та електротехніки...

Если Вам нужно дополнительный материал на эту тему, или Вы не нашли то, что искали, рекомендуем воспользоваться поиском по нашей базе работ: Схемна реалізація логічних функцій на прикладі функцій “НЕ”, “І”, “АБО”, 3І–НЕ”, “3АБО–НЕ” та ін.

Что будем делать с полученным материалом:

Если этот материал оказался полезным ля Вас, Вы можете сохранить его на свою страничку в социальных сетях:

| Твитнуть |

Хотите получать на электронную почту самые свежие новости?

Новости и инфо для студентов