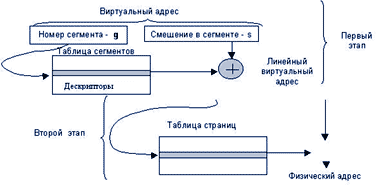

Сегментное - страничное распределение

Данный метод представляет собой комбинацию страничного и сегментного механизмов управления памятью и направлен на реализацию достоинств обоих подходов.

Виртуальная память делится на сегменты, а каждый сегмент - на страницы.

Все современные ОС используют именно такой способ организации.

Рис.16 Схема преобразования виртуального адреса в физический при сегментно - страничном распределении.

42. Схема управления ОП в МП семейства Intel 80x86

http://upload.wikimedia.org/wikipedia/ru/thumb/c/cf/8086_adress.png/799px-8086_adress.png

Таким образом, память разделяется на сегменты, размером 64 Кбайт каждый и начинающиеся с адреса, кратного 16; память в 1 Мбайт разделялась, таким образом, на 16 сегментов. Эти 16 сегментов называют страницами памяти.

43 Дескрипторные таблицы — служебные структуры данных, содержащие дескрипторы сегментов.

В архитектуре x86 есть три вида дескрипторных таблиц:

· Глобальная дескрипторная таблица (англ. Global Descriptor Table, GDT);

· Локальная дескрипторная таблица (англ. Local Descriptor Table, LDT);

· Таблица векторов прерываний (англ. Interrupt Descriptor Table, IDT);

Глобальная дескрипторная таблица

Основная статья: GDT

Глобальная дескрипторная таблица является общей для всех процессов. Её размер и расположение в физической памяти определяются регистром GDTR. Размер таблицы не может превышать 8192 дескрипторов, поскольку один дескриптор занимает 8 байт, а лимит в регистре GDTR — двухбайтный и хранит размер таблицы минус один (максимальное значение лимита — 65535), а 8192 x 8 = 65536.

Дескрипторы LDT и сегментов задач (TSS) могут находиться только здесь.

Особенностью GDT является то, что у неё запрещён доступ к первому (с нулевым смещением относительно начала таблицы) дескриптору. Обращение к нему вызывает исключение#GP, что предотвращает обращение к памяти с использованием незагруженного сегментного регистра.

Локальная дескрипторная таблица

В отличие от GDT, LDT может быть много (соответственно количеству задач (потоков), но не обязательно). Каждая задача может иметь свою. На расположение таблицы текущей задачи указывает регистр LDTR.

Размер и расположение LDT в линейной памяти определяются дескриптором LDT из GDT (но это не означает, что размер LDT может быть больше 65536 байт).

Первый дескриптор LDT (№ 0) использовать можно.

Таблица дескрипторов прерываний

Основная статья: Таблица векторов прерываний

Таблица прерываний глобальна. Размещение в физической памяти определяется регистром IDTR.

При возникновении прерывания (внешнего, аппаратного, или вызванного инструкцией Int):

· из IDT выбирается дескриптор шлюза, соответственно номеру прерывания;

· проверяются условия защиты (права доступа);

· при соблюдении условий защиты выполняется переход на подпрограмму-обработчик этого прерывания.

44 Формат дескриптора сегмента МП i80286

БД- байт доступа содержит тип сегмента привилегий R или W

45 Формат байта доступа дескриптора сегмента

· Бит P определяет доступность сегмента (0 — сегмента нет, 1 — есть).

· Номер привилегий DPL содержит 2-битный номер (0-3), определяющий, к какому уровню (кольцу) защиты относится этот сегмент.

· Тип сегмента, cтарший бит (S) определяет сегмент как системный (S=0) или пользовательский (S=1)

| P |

DPL тип A (доступ к сегменту)

Типы: сегмент кода(11),сегмент данных(10), LDT(00)

31 15 0

| Селектор сегмента | смещение |

Адрес:

46 Причины нарушений защиты памяти

1 – попытка записи в сегмент кода

2 – запрет чтения сегмента кода

3 – запрет записи в сегмент данных

4 - попытка обращения за пределы сегмента

5 – попытка обращения к сегменту LDT

6 – недостаточность привилегий прграммы

для обращения к данным сегмента

47 Кольца защиты

Процессор i80286 использует более гибкую и надёжную схему защиты операционной системы и программ друг от друга.

В этой схеме используются привилегии четырёх уровней - от 0 до 3. Самые большие привилегии соответствуют уровню 0. Обычно такими привилегиями обладает ядро операционной системы. Минимальные привилегии у пользовательских программ - уровень 3.

Уровни привилегий часто называют кольцами защиты (см. рис. 10).

Рис. 10. Кольца защиты.

Как распределить привилегии программ в операционной системе? Можно использовать, например, такое распределение:

- Кольцо 0 - ядро операционной системы, системные драйверы. Привилегированное кольцо. Содержит код и данные операционной системы

- Кольцо 1 - программы обслуживания аппаратуры, драйверы, программы, работающие с портами ввода/вывода компьютера. В ОС Windows не поддерживается

- Кольцо 2 - системы управления базами данных, расширения операционной системы. В ОС Windows не поддерживается

· Кольцо 3 - прикладные программы, запускаемые пользователем. непривелигированное кольцо. Содержит

код и данные пользовательских программ

Программа будет предоставлять доступ к сегментам только в случае, когда уровень привилегий дескриптора запрашиваемого сегмента DPL больше или равен наибольшему из значений текущего уровня привилегий CPL и уровня запрашиваемых привилегий RPL:

DPL ≥ max(CPL, RPL)

Если программа попытается получить доступ к более привилегированному сегменту памяти, чем она сама, её выполнение будет прервано.

48 Блок управления памятью или устройство управления памятью (англ. memory management unit, MMU) — компонент аппаратного обеспечения компьютера, отвечающий за управление доступом к памяти, запрашиваемым центральным процессором. Его функции заключаются в трансляции адресов виртуальной памяти в адреса физической памяти (то есть управление виртуальной памятью), защите памяти, управлении кеш-памятью, арбитражем шины и, в более простых компьютерных архитектурах (особенно 8-битных), переключением блоков памяти. Иногда также упоминается как блок управления страничной памятью (англ. Paged memory management unit, PMMU)

В настоящее время, чаще всего, упоминается в связи с организацией т. н. виртуальной памяти и, следовательно, критически важен для многих современных многозадачныхоперационных систем, включая все современные Windows NT и многие из UNIX‐подобных. Специальная редакция ядра Linux, μClinux, может работать без MMU.

Блок управления памятью в настоящее время очень часто включается в состав центрального процессора или чипсета компьютера.

Принципы работы

Принцип работы современных MMU основан на разделении виртуального адресного пространства (одномерного массива адресов, используемых центральным процессором) на участки одинакового, как правило несколько килобайт, хотя, возможно, и существенно большего, размера равного степени 2, называемые страницами. Младшие n бит адреса (смещение внутри страницы) остаются неизменными. Старшие биты адреса представляют собой номер (виртуальной) страницы. MMU обычно преобразует номера виртуальных страниц в номера физических страниц используя буфер ассоциативной трансляции (англ. Translation Lookaside Buffer, TLB). Если преобразование при помощи TLB невозможно, включается более медленный механизм преобразования, основанный на специфическом аппаратном обеспечении или на программных системных структурах. Данные в этих структурах как правило называются элементами таблицы страниц (англ. page table entries (PTE)), а сами структуры — таблицами страниц (англ. page table, PT). Конкатенация номера физической страницы со смещением внутри страницы дает физический адрес.

Элементы PTE или TLB могут также содержать дополнительную информацию: бит признака записи в страницу (англ. dirty bit), время последнего доступа к странице (англ. accessed bit, для реализации алгоритма замещения страниц наиболее давно использованный (англ. least recently used, LRU), какие процессы (пользовательские (англ. user mode) или системные(англ. supervisor mode)) могут читать или записывать данные в страницу, необходимо ли кэшировать страницу

49 Логический(виртуальный) адрес

ОП

Ofs 32 32

| |||

|

Т Линейный

Т Линейный

база адрес

база адрес

|

Физический адрес

Физический адрес

Таблица страниц

Таблица каталогов