Структура діодних ключей та їх статичні характеристики

Зміст

Зміст

1. Теоретична частина ……………………………………………………

1.1 Діодні ключі та обмежувачі……………………………..……

Структура діодних ключей та їх статичні характеристики

передачі………………………………………………………

Послідовний діодний ключ…………......................................

Паралельний діодний ключ……….……................................

Двосторонній обмежувач…………………………………..

2 Контрольні запитання………………………………………………………

3 Задачі… ………………………………..………………………………..….

4 Приклад виконання завдання………………………………………….…..

5 Список використаних джерел…………………………………….….........

1. ТЕОРЕТИЧНА ЧАСТИНА

ДІОДНІ КЛЮЧІ

Структура діодних ключей та їх статичні характеристики передачі

На практиці при будуванні діодних ключей найбільше pозповсюдження отримали послідовна й паралельна СК. Тому зупинимося на розгляді властивостей…Послідовний діодний ключ

Рис. 1 Схема послідовного діодного ключа

, для

, для

та

, для

, для

де rд пр, rд обр, Uд0 – параметри кусочно-лінійної апроксимації ВАХ—диференціальні опори при прямому та зворотному зсуві p-n-переходу і порогова напруга відповідно.

За умови, що діод і джерело вхідного сигналу ідеальні ( rдпр=0, rд овр=∞ і Rвн=0), система рівнянь прийме вигляд:

Uвих =  , для

, для

Uвих = 0, для

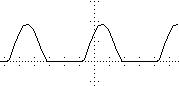

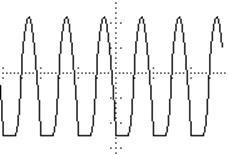

Відповідно до отриманих виразів, часові діаграми вхідного та вихідного сигналів послідовного діодного ключа має вигляд, що показаний на рис. 2а,б.

а) б)

Рис.2 Діаграми вхідного (а) та вихідного (б) сигналів для схеми Рис. 1

В випадку реальних діода та джерела сигнала амплітуда вихідного сигналу буде нижча за амплітуду вхідного сигналу за рахунок спаду напруги на діоді.

Вигляд часової діаграми можна змінювати, якщо до схеми ключа ввести допоміжні джерела зсуву Ecм. Можливі варіанти таких схем наведені на рис.3а,б

а) б)

Рис. 3 Схеми з зсувом вихідного сигналу

В обохсхемах напруга включення визначається виразом eвкл =Uдо + Uсм. Значення Uсм залежить від місця включения допоміжного джерела. Так, для схеми рис. 3,а Uсм = EcмRн/(Rcм+Rн), а для схеми рис. 3б Uсм = Есм. Наведемо часові діаграми для цих двох схем:

a) б)

Рис. 4 часові діаграми до рис. 3а) ,б)

Паралельний діодний ключ

Рис. 6 Схема паралельного діодного ключа та його часова діаграма

Завдяки діоду вихідна напруга не може перевищувати напругу Е (якщо діод ідеальний), при цьому присутність діоду ніяк не впливає на менші значення напруги (в тому числі і на від’ємних); єдина умова полягає у тому, що від’ємна вхідна напруга не повинна досягати значення напруги пробою (наприклад, для діода 1N914 це значення досягає -70В). В усіх схемах цифрових логічних КМОП-схем використовуються вхідні діодні обмежувачі. Вони охороняють ці чуттєві схеми від руйнування під дією розрядів статичного електрика.

Еталонну опорну напругу можна подавати на обмежувач від дільник напруги (Рис. 7а). Якщо дільник напруги замінити його еквівалентною схемою, то вихідна схема перетвориться до виду що представлений на рис. 7б. Аналізуючи перетворену схему, можна заключити, що імпеданс зі сторони виходу дільника напруги (Rділ) повинен бути малим в порівнянні з опором R. Коли діод відкритий (вхідна напруга перевищує напругу обмежувача), вихідна напруга співпадає з напругою, що береться з дільника, при цьому нижнє плече дільника представлено еквівалентним опором.

1.1.4 Двосторонній обмежувач

Ще один обмежувач показан на рис. 8. Ця схема обмежує “розмах” вихідного сигналу та робить його рівним падінню напруги на діоді, тобто приблизно 0,6В. Може здаватися, що це дуже мала напруга, але якщо наступним каскадом схеми є підсилювач з великим коефіцієнтом підсилювання за напругою, то вхідний сигнал для нього завжди повинен бути декілька більше ніж 0В, інакше підсилювач попадає до режиму “насичення” (наприклад, якщо коефіцієнт підсилювання каскаду рівний 1000, а живлення складає ±15В, то вхідний сигнал не повинен перевищувати діапазон ±15мВ). Описана схема часто використовується в якості захисту на вході підсилювача з великим коефіцієнтом напруги. Іноді замість діодів в цій схемі використовуються стабілітрони.

Промоделюємо цю схему у пакеті EWB5:

Промоделюємо цю схему у пакеті EWB5:

Рис. 9

2. КОНТРОЛЬНІ ПИТАННЯ

1. Для чого використовуються діодні ключі сигналів?

2. Чим відрізняються послідовні та паралельні ключі в схемі? А на діаграмі?

3. Пояснити призначення резистора Rб у схемі на рис. 5а та в інших схемах у даному розділі.

4. Як впливає резистор R у схемах на рис. 3а) та 3б) на вихідний сигнал?

5. Як зміниться вихідний сигнал, якщо в схемі, що представлена на рис. 6, поміняти полярність діода?

6. Як зміниться вихідний сигнал, якщо в схемі, що представлена на рис. 6, замість ідеального діода взяти реальний, наприклад 1N4305 (Uпр=0,6В)?

7. Як зміниться вихідний сигнал, якщо в схемі, що представлена на рис. 6, збільшити напругу Е?

8. Пояснити призначення двостороннього обмежника та побудувати його часову діаграму.

3. задачі

1. Зібрати схему обмежувача сигналів, якщо верхня межа вихідних сигналів повинна бути на рівні N В. Використати реальний діод (його номер у таблиці обчислюється за формулою N mod 4). Uвх лежить в межах ±30В. Привести часові діаграми вхідного та вихідного сигналів. N – порядковий номер студента в журналі групи.

2. Зібрати схему обмежувача сигналів, якщо нижня межа вихідних сигналів повинна бути на рівні N/2 В. Використати реальний діод (його номер у таблиці обчислюється за формулою N mod 4). Uвх лежить в межах ±30В. Привести часові діаграми вхідного та вихідного сигналів. N – порядковий номер студента в журналі групи.

3. Запропонуйте схему двостороннього обмежника, у якого вихідна напруга змінюється в діапазоні від –N/2 В до N В. Uвх лежить в межах ±30В. Привести часові діаграми вхідного та вихідного сигналів. N – порядковий номер студента в журналі групи.

4. Побудувати схему обмежника сигналів з використанням резистора 5 кОм, стабілітронів (КС133, КС142, КС147) з обмеженням напруги на рівні 10*N/3 В. Вибрати стабілітрон, що найбільше підходить для побудування заданої схеми. Привести часові діаграми вхідного та вихідного сигналів. N – порядковий номер студента в журналі групи.

| Таблиця 1. Типи діодів | |||||

| № діода | Тип діода | Uпр, В | Uзвор, В | Іпр, мА | Ізвор, мА |

| 1N4305 | 0.6 | ||||

| 1N4002 | 0.9 | ||||

| 1N4007 | 0.9 | ||||

| 1N5625 | 1.1 |

4. ПРИКЛАД ВИКОНАННЯ ЗАВДАННЯ

Завдання: на рис. 10 приведена схема обмежувача сигналів верхнього рівня. Uвх лежить в межах ±15В. Необхідно розрахувати параметри схеми, якщо нижня межа сигналів повинна бути 3В. Привести часові діаграми вхідних та вихідних сигналів. Діод взяти 1N4002.

Рішення:

Якщо на виході повинно бути 3В, то Е + Uд = 3В. Uд = 0,9В (за таблицею), тоді Е = 3 – 0,9 = 2,1В.

Опір R потрібен, щоб обмежувати струм на діоді. Ід мах = 50 мкА, Uвх мах = 15В, тоді R=

Опір R потрібен, щоб обмежувати струм на діоді. Ід мах = 50 мкА, Uвх мах = 15В, тоді R= =

= = 0,3 *106 = 300 кОм.

= 0,3 *106 = 300 кОм.

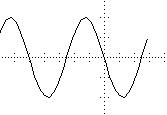

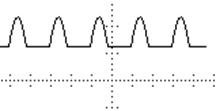

Будуємо часові діаграми сигналів:

Будуємо часові діаграми сигналів:

Часова діаграма вхідного сигналу Часова діаграма вихідного сигналу

ЛІТЕРАТУРА

1. Хоровиц П., Хилл У. Искусство схемотехники М.:Мир 1том, 2004-598с.

2. Титце У. ,Шенк К. Полупроводниковая схемотехника М.:Мир, 2001-512с.

3. Баюков А. В., Гитцевич А. Б., Зайцев А. А.,Мокряков В. В. Полупроводниковые приборы М: Энергоатомиздат, 2000-744с

|