Особливості структурної організації

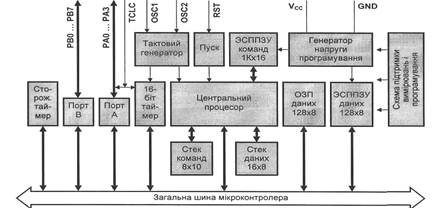

МікроконтролерКР1878ВЕ1 містить в собі слідуючі функціонально закінчені пристрої (рис. 9.1): центральний процесор, ЕППЗП команд, ОЗП даних, ЕППЗП даних-констант, сторожовий таймер, 2 порти вводу/виводу і таймер загального призначення.

Рис. 9.1. Структурна схема мікроконтролера КР1878ВЕ1

Обмін даними між центральним процесором, ОЗП даних і периферійними пристроями відбувається по єдиній шині. Конструктивно КР1878ВЕ1 сумісний з подібними мікроконтролерами фірм Microchip та Zilog.

9.1.3. Центральний процесор

Архітектура процесора Аn15ЕОЗ характеризується поділеною пам'яттю команд і даних. Це дозволяє сумістити процеси вибірки команд і вибірки операндів з пам'яті.

Система команд процесора симетрична – є двохоперандні команди, що працюють водночас з двома операндами. Вибірка операндів з пам'яті даних у випадку двохоперандних команд здійснюється водночас по двох різних шинах – даних SRC операнда і даних DST операнда, з окремими шинами адрес.

Запис результату в пам'ять здійснюється також по окремій шині запису даних. Адреса запису суміщена з адресою читання операнда DST.

Команди процесора мають розмірність 16 розрядів. Для забезпечення механізмів переходу до підпрограм і переривань програм в процесорі існує окремий апаратний стек глибиною у вісім адрес, де зберігаються адреси повернення з підпрограм і переривань.

У процесорі є службові регістри для підтримки методу адресації операндів. Для збереження значень цих регістрів і слова стану процесора при перериваннях програм і переходів до підпрограм введений окремий апаратний стек даних глибиною в 16 байтів. Звернення до регістрів периферійних приладів МК відбувається по тих же шинах і точно так само, як і до оперативної пам'яті.

На різних стадіях виконуються три команди процесора.