Універсальні регістри

У серіях ИС і бібліотеках БІС/СБИС програмувальної логіки мається багато варіантів регістрів (у схемотехнике ТТЛШ їх близько 30). Серед них багаторежимні (багатофункціональні) чи універсальні, здатні виконувати набір мікрооперацій. Багаторежимність досягається композицією в одній і тій же схемі частин, необхідних для виконання різних операцій. Керуючі сигнали, що задають вид виконуваної тепер операції, активізують необхідні для цього частини схеми.

Таблиця 1.1

| Режим | Входы | Выходы |

| C R S0 S1 DSR DSL Dn | Q0 Q1 … Q6 Q7 | |

| Сброс | X L X X X X X | L L … L L |

Хранение Хранение

| H L L X X X | Q0 Q1 … Q6 Q7 |

Сдвиг

влево Сдвиг

влево

| H H L X L X H H L X H X | Q1 Q2 … Q7 L Q1 Q2 … Q7 H |

Сдвиг

вправо Сдвиг

вправо

| H L H L X X H L H H X X | L Q1 … Q5 Q6 H Q1 … Q5 Q6 |

Параллельная

загрузка Параллельная

загрузка

| H H H X X Dn | D0 D1 … D6 D7 |

Типовим представником багаторежимних регістрів є мікросхема ИР13 серії КР1533 і інших (рис. 1.6). Це восьмиразрядный регістр із можливістю двосторонніх зрушень із припустимою тактовою частотою до 25 МГц при струмі споживання до 40 мА. Має також рівнобіжні входи і виходи, вхід асинхронного скидання R і входи вибору режиму S0 і S1, що задають чотири режими (рівнобіжне завантаження, два зрушення і збереження). Функціонування регістра визначається табл. 1.1.

Умовна позначка регістра ИР13 приведене на рис. 1.5.

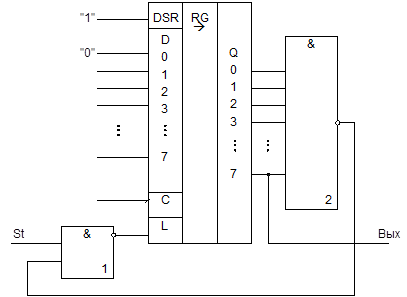

Регістри, що мають різнотипні вхід і вихід, служать основними блоками перетворювачів рівнобіжних кодів у послідовні і назад. На рис. 1.7 показана схема перетворювача рівнобіжного коду в последоватсльнып на основі восьмиразрядного регістра типу SI/PI/SO. У цій схемі негативний стартовий імпульс St, що задає рівень логічного нуля на верхньому вході елемента 1, створює одиничний сигнал рівнобіжного прийому даних на вхід L (Load — завантаження), по якому в розряди 1...7 регістра завантажується преутворене слово D1-7, а в нульовий розряд — константа 0. На послідовний вхід DSR. подано константу 1.

|

Рис. 1.5 УГО унiверсальго регiстра

|

Рис. 1.6 Схема богаторежимного регистра

Таким чином, після завантаження в регістрі формується слово 0D1D2...D7. Тактові імпульси, що надходять на вхід З, викликають зрушення слова вправо (для умовної позначки це відповідає зрушенню вниз). Зрушення виводять слово в послідовній формі через вихід (Q7. Слідом за інформаційними розрядами йде нуль (константа "0"), після якого ланцюжок одиниць. Поки нуль не виведений з регістра, на виході елемента 2 діє одиничний сигнал. Після висновку нуля усі входи елемента 2 стають одиничними, його вихід здобуває нульове значення і через елемент 1 формує сигнал автоматичного завантаження наступного слова, після чого цикл перетворення повторюється.

|

Рис 1.7 Схема перетворювача рівнобіжного коду в послідовний

У переліку мікрооперацій, виконуваних регістрами, минулого зазначені поразрядные логічні операції. Сучасні регістри мало пристосовані для виконання ці операції, однак при необхідності їх можна виконати, користаючись регістрами на RS-тригерах. Для виконання ЧИ операції на S-входи статичного регістра з вихідним нульовим станом подається перше слово А, одиничні розряди якого установлюють відповідні тригери. Потім без скидання регістра на S-виходи подається друге слово В. Ясно, що в результаті одержимо результат Q = АÚВ.

При виконанні поразрядной операції И в першому такті на S-входи регістра подасться слово А, що встановлює ті розряди регістра, у яких слово А має одиниці. Потім варто подати на регістр слово В. Щоб у регістрі збереглися одиниці тільки в тих розрядах, у яких одиниці мають обоє слова, слово В подається на входи R тригерів в інверсному виді.

Додавання по модулі 2 може бути виконано схемою з тригерами типу Т в розрядах шляхом послідовної в часі подачі на неї двох слів А и В.