рефераты конспекты курсовые дипломные лекции шпоры

- Раздел Образование

- /

- Вид работы: Отчеты по Практике

- /

- Алгоритм работы

Реферат Курсовая Конспект

Алгоритм работы

Алгоритм работы - Отчет по Практике, раздел Образование, ОТЧЕТ ПО УЧЕБНОЙ ПРАКТИКЕ Пояснительная записка - Деление На Счетчике Частоты 25Mhz На 2**23; - Пооч...

- деление на счетчике частоты 25Mhz на 2**23;

- поочередное включение (активный уровень – логический нуль)/выключение светодиодов при помощи счетчика –дешифратора (0-7).

В САПР Quartus II создать новый проект.

В таблице 5.1 приведены параметры мастера

В таблице 5.1 приведены параметры мастера

Таблица 5.1 – Параметры мастера

| Параметр мастера | Наименоваение |

| What is the working directory for this project? Рабочая папка ( с помощью браузера найти рабочую папку проекта) | … begushiy |

| What is the name of this project? Имя проекта | begushiy |

| What is the name of the top-level design entity for this project? Имя модуля верхнего уровня в иерархии проекта. | begushiy |

В окне Family & Device Setting выбрать:

- в разделе Family задать Cyclone III;

- тип корпуса в графе Package задать – TQFP;

- в графе Pin count задать - 144,

- в разделе Available devicesвыбрать СБИС EP3C5E144C8.

Во вновь созданном проекте, именуемом «begushiy» необходимо создать новый файл «File –New – Block Diagram/Schematic File».

Во вновь созданном проекте, именуемом «begushiy» необходимо создать новый файл «File –New – Block Diagram/Schematic File».

Сохранить файл под тем же именем что и проект.

Вызвать мастер Mega Wizard Plug-in Manager, через меню Tools – Mega Wizard Plug-in Manager.

В окне 1 выбрать «Create a new custom megafunction variatrion»

В окне 2 перейти в раздел Arithmetic, выбрать пункт LPM_COUNTER, задать имя выходного файла, count, в качестве языка описания выбрать VHDL, нажать кнопку Next

Проектируется суммирующий счетчик с максимальным количеством перебора 33 554 432.

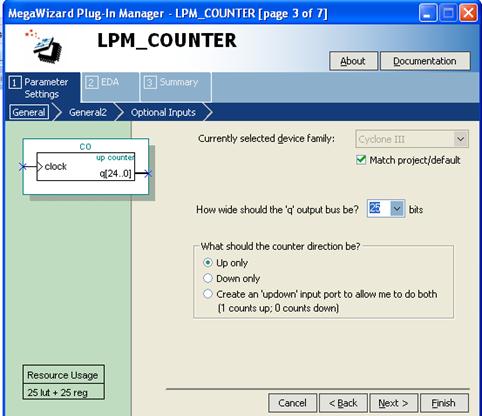

Параметры счетчика:

- ширина шины q = 25 бит;

- счетчик суммирующий «up only»

По окончании нажать Next

На рисунке 5.1 представлено окно с параметрами, которые нужно задать.

Рисунке 5.1– Окно с параметрами

На рисунке 5.2 представлено окно параметров счета, входов управления счетом, флагов переноса .

.

Рисунок 5.2– Окно параметров счета

В появившемся окне «Optional Inputs» осуществляется назначение синхронных/ асинхронных входов загрузки, сброса, установки в максимальное значение. Все эти опции оставить пустыми. Нажать Next дважды.

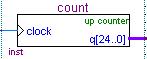

Нажать Finish. В рабочей библиотеке появился компонент count.

На рисунке 5.3 представлен синтезированный компонент.

Рисунок 5.3– Синтезированный компонент

Далее необходимо создать второй счетчик со встроенным дешифратором от 0 до 7, к которому будут подключены светодиоды [led 0-7]. Данный элемент следует описать на языке VHDL, для этого необходимо в меню File-New выбрать VHDL File. В открывшемся окне набрать следующий код, реализующий функцию дешифратора согласно заданию. Имя модуля - led.vhd.

В листинге 1 представлен описываемый компонент.

Листинг 1- led.vhd

LIBRARY.IEEE;\

use IEEE.std_logic_1164.all;\

use IEEE.std_logic_unsigned.all;\

use IEEE.numeric_std.ALL;\

entity led is port\

(clk: in std_logic;\

led: out std_logic_vector(7 downto 0));\

end led;\

architecture led_arch of led is\

signal cnt: integer range 0 to 7 :=0;\

begin\

process (clk)\

begin\

if rising_edge(clk) then\

if cnt=7 then\

cnt<=0;\

else\

cnt<=cnt+1;\

end if;\

end if;\

end process;\

led(0)<= '1' when cnt=0 else '0';\

led(1)<= '1' when cnt=1 else '0'; \

\

led(2)<= '1' when cnt=2 else '0';\

led(3)<= '1' when cnt=3 else '0';\

led(4)<= '1' when cnt=4 else '0';\

led(5)<= '1' when cnt=5 else '0';\

led(6)<= '1' when cnt=6 else '0';\

led(7)<= '1' when cnt=7 else '0';\

end led_arch;\

Выполнить команд меню File- Create/Update – Create Symbol Files for Current File. В библиотеке появится новый компонент с именем led.

На рисунке 5.4 представлен синтезированный элемент.

Рисунок 5.4– Синтезированный элемент- led

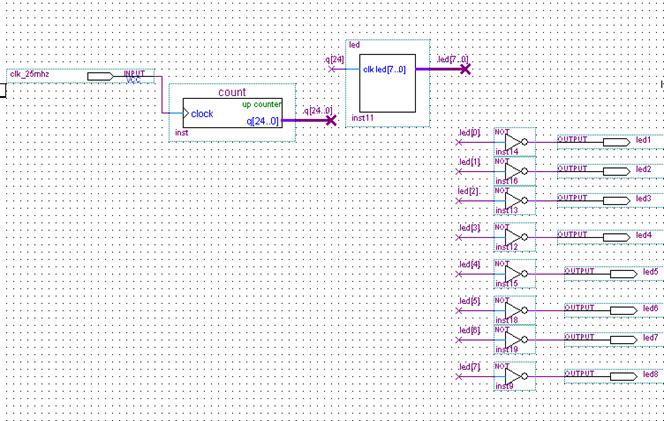

На рисунке 5.5 представлена синтезированная схем, реализуемая при помощи схемного проектирования.

На рисунке 5.5 представлена синтезированная схем, реализуемая при помощи схемного проектирования.

|

Рисунок 5.5– Синтезированная схема

Далее необходимо осуществить проверку синтаксиса схемы. Для этого в меню Processing выполнить команду Start=>Start Analysis & Elaboration.

Далее необходимо осуществить проверку синтаксиса схемы. Для этого в меню Processing выполнить команду Start=>Start Analysis & Elaboration.

Перейти в инструмент Assignments - Pin Planner и выполнить назначение выводов на СБИС (ПЛИС) выводам схемы, как показано на рисунке 5.6.

Рисунок 5.6– Назначение выводов на СБИС

С помощью команды Processing => Start Compilationосуществить полную компиляцию проекта.

Конфигурирование платы:

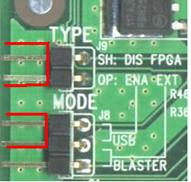

- На плате miniDiLaB-CIII установить джамперы следующим образом (рисунок 5.7):

a. Соединить выводы разъема “TYPE”

b. Соединить выводы 1-2 разъема “MODE”

Рисунок 5.7– Установка джамперов

Подсоединить, входящий в комплект поставки USB кабель A-miniB к USB 2.0 порту компьютера (должен обеспечивать ток до 500мА), а затем к плате miniDiLaB-CIII.

Выполнить команду Tools=> Programmerили кликнуть по значку главного меню (рисунок 5.8)

Выполнить команду Tools=> Programmerили кликнуть по значку главного меню (рисунок 5.8)

Рисунок 5.8– Главное меню

Откроется окно управления конфигурированием СБИС.

Для установки интегрированного на плату miniDiLaB-CIII средства конфигурирования СБИС нажать кнопку Hardware Setup,откроется окно настроек в нем выбрать USB- Blaster.

Светодиод led[7..0], для которого разрешена работа (счетчик содержит значение данного светодиода ) будет светится и гаснуть, следующим загорится светодиод номер которого будет следующим.

5.2 Вывод

5.2 Вывод

В результате выполнения задания спроектировано цифровое устройство, выполняющее поочередное включение /выключение светодиодов. Проведено описание работы элемента на языке VHDL, синтезирован компонент, как представлено на рисунке 5.4 на плате DiLaB – III (Cyclone III); проведена отладка и проверка работоспособности схемы.

В результате выполнения можно дать определение дешифратору как устройству, с несколькими входами и выходами, которое преобразует код, подаваемый на входы в сигнал на одном из выходов.

Назначение вывода Carry –out- выход сигнала переноса,

Назначение вывода Set-установка параметра,

Назначение вывода Load- загрузка данных.

Изменение кода описания счетчика-дешифратора, чтобы «бегущий огонь» начинался с led 7 и шел до led 0:

led(0)<= '1' when cnt=7 else '0';

led(1)<= '1' when cnt=6 else '0';

led(2)<= '1' when cnt=5 else '0';

led(3)<= '1' when cnt=4 else '0';

led(4)<= '1' when cnt=3 else '0';

led(5)<= '1' when cnt=2 else '0';

led(6)<= '1' when cnt=1 else '0';

led(7)<= '1' when cnt=0 else '0'

– Конец работы –

Эта тема принадлежит разделу:

ОТЧЕТ ПО УЧЕБНОЙ ПРАКТИКЕ Пояснительная записка

ОП ПЗ ОГБОУСПО ИАТ ОТЧЕТ ПО УЧЕБНОЙ ПРАКТИКЕ...

Если Вам нужно дополнительный материал на эту тему, или Вы не нашли то, что искали, рекомендуем воспользоваться поиском по нашей базе работ: Алгоритм работы

Что будем делать с полученным материалом:

Если этот материал оказался полезным ля Вас, Вы можете сохранить его на свою страничку в социальных сетях:

| Твитнуть |

Хотите получать на электронную почту самые свежие новости?

Новости и инфо для студентов