Алгоритм работы

В САПР Quartus II создать новый проект .

.

В таблице 6.1 приведены параметры мастера

Таблица 6.1 – Параметры мастера

| Параметр мастера | Наименование |

| What is the working directory for this project? Рабочая папка ( с помощью браузера найти рабочую папку проекта) | … crypto |

| What is the name of this project? Имя проекта | crypto |

| What is the name of the top-level design entity for this project? Имя модуля верхнего уровня в иерархии проекта. | crypto |

В окне Family & Device Setting выбрать:

- в разделе Family задать Cyclone III;

- тип корпуса в графе Package задать – TQFP;

- в графе Pin count задать - 144,

- в разделе Available devicesвыбрать СБИС EP3C5E144C8

По окончанию создания проекта, создать новый файл Block Diagram/Schematic File. Сохранить файл под тем же именем что и проект.

Вызвать мастер Mega Wizard Plug-in Manager, через меню Tools – Mega Wizard Plug-in Manager.

В окне 1 выбрать «Create a new custom megafunction variatrion»

В окне 2 перейти в раздел Arithmetic, выбрать пункт LPM_COUNTER, задать имя выходного файла, count, в качестве языка описания выбрать VHDL, нажать кнопку Next

Задать ширину шины q =20 бит. На рисунке 6.2 представлено окно с параметрами, которые необходимо задать:

- ширина шины q = 20 бит;

- счетчик суммирующий «up only»

По окончании нажать Next

Рисунок 6.2– Окно с параметрами

Рисунок 6.2– Окно с параметрами

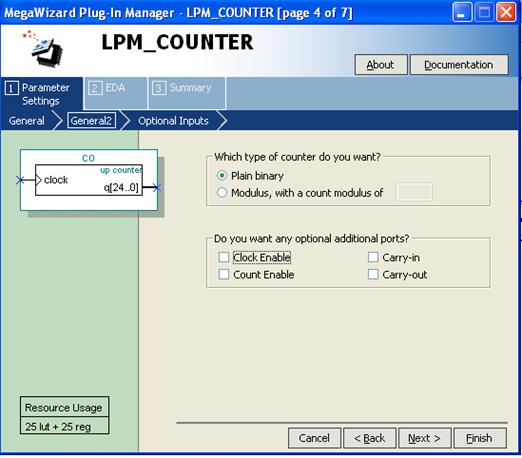

На рисунке 6.3 представлено окно параметров счета, входов управления счетом, флагов переноса .

.

Рисунок 6.3– Окно параметров счета

В появившемся окне «Optional Inputs» осуществляется назначение синхронных/ асинхронных входов загрузки, сброса, установки в максимальное значение. Все эти опции оставить пустыми. Нажать Next дважды.

Нажать Finish. В рабочей библиотеке появился компонент count.

На рисунке 6.4 представлен синтезированный компонент.

Рисунок 6.4– Синтезированный компонент

Далее необходимо создать 8 –разрядный последовательно – параллельный сдвиговый регистр, с входом синхронизации и разрешением работы .

.

Библиотечный элемент расположен в Storage Installed Plug-In. В таблице 6.2 приведены значения параметров регистра, которые необходимо выставить. Данный элемент следует создать по аналогии с предыдущим.

Таблица 6.2 – Значения параметров регистра

| Параметр мастера | Наименование |

| Which direction do you want the register to shift? Определить направление сдвига | Right (сдвиг вправо) |

| How wide should the ‘q’ output bus be Ширина шины данных выхода , бит | |

| Which outputs do you want? Какой тип шины выхода данных. | Data output (параллельный выход) |

| Do you want any optional inputs? Какие дополнительные входы выбрать? | Clock Enable input (вход управления - синхронизация) Serial shift data input Последовательный вход данных |

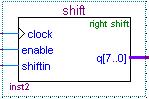

На рисунке 6.5 представлен компонент сдвигового регистра.

Рисунок 6.5– Синтезированный компонент

На рисунке 6.6 представлена синтезированная схема, реализующая формирование псевдослучайных последовательностей.

На рисунке 6.6 представлена синтезированная схема, реализующая формирование псевдослучайных последовательностей.

|

Рисунок 6.6– Синтезированная схема

Далее необходимо осуществить проверку синтаксиса схемы. Для этого в меню Processing выполнить команду Start=>Start Analysis & Elaboration.

Далее необходимо осуществить проверку синтаксиса схемы. Для этого в меню Processing выполнить команду Start=>Start Analysis & Elaboration.

Перейти в инструмент Assignments - Pin Planner и выполнить назначение выводов на СБИС (ПЛИС) выводам схемы, как показано на рисунке 6.7.

Рисунок 6.7– Назначение выводов на СБИС

С помощью команды Processing => Start Compilationосуществить полную компиляцию проекта.

Конфигурирование платы:

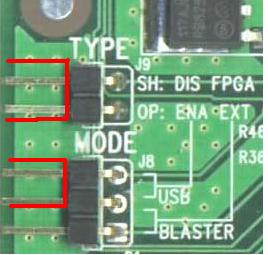

На плате miniDiLaB-CIII установить джамперы следующим образом (рисунок 6.8):

a. Соединить выводы разъема “TYPE”

b. Соединить выводы 1-2 разъема “MODE”

Рисунок 6.8– Установка джамперов

Выполнить команду Tools=> Programmerили кликнуть по значку главного меню (рисунок 6.9)

|

Рисунок 6.9– Главное меню

Откроется окно управления конфигурированием СБИС.

Для установки интегрированного на плату miniDiLaB-CIII средства конфигурирования СБИС нажать кнопку Hardware Setup,откроется окно настроек в нем выбрать USB- Blaster.

Светодиоды led[4..1], будут загораться в некотором порядке при нажатии на кнопку PBA. При опускании кнопки РВА светодиоды будут гореть, что соответствует некоторому псевдослучайному числу. При повторном нажатии на кнопку PBA, состояние светодиодов изменится.

6.2 Вывод

6.2 Вывод

В результате выполнения задания спроектировано цифровое устройство, выполняющее формирование псевдослучайных последовательностей.

Проведено описание работы элемента на языке VHDL, синтезированы компоненты, как представлено на рисунках 6.4, 6.5 на плате DiLaB – III (Cyclone III); проведена отладка и проверка работоспособности схемы.

Генератор случайных чисел встречается в нашей жизни повсеместно. По принципу генерирования случайных чисел работают игровые автоматы. При скачивании файлов с Интернета также сталкиваемся с этим принципом, вводя случайный код для проверки. В социальных сетях, электронной почте также генерируются случайные пароли. Область применений случайных чисел огромна, их используют при создании видео игр, при написании программ и тд.

Закон формирования псевдослучайной последовательности для данной схемы:

Y=((R1[Q4] XOR R1[Q8]) XOR R2[Q2]) XOR R1[Q5]

Заключение

Заключение

В ходе выполнения работы был изучен язык VHDL в достаточно полном объеме – пройден процесс проектирования от постановки задачи до реализации работающего устройства в системе Quartus II.

Язык проектирования VHDL является базовым языком при разработке аппаратуры современных вычислительных систем. Этот язык набирает популярность, так как обеспечивает весьма эффективное моделирование на уровне интегральных схем и не сложен в изучении.

Список используемой литературы

Список используемой литературы

1. Сергиенко А.М.«VHDL для проектирования вычислительных устройств».

2. Поляков А.К. «Языки VHDL и VERILOG в проектировании аппаратуры».

3. Практикум: учебное пособие / Ф.А. Губарев,О.И. Андрющенко.

4. Ф.А. Губарев, О.И. Андрющенко «ЦИФРОВЫЕ УСТРОЙСТВ».