рефераты конспекты курсовые дипломные лекции шпоры

- Раздел Компьютеры

- /

- В настоящее время существуют два типа архитектуры микропроцессорных систем – Принстонская, или архитектура фон-Неймана и Гарвардская

Реферат Курсовая Конспект

В настоящее время существуют два типа архитектуры микропроцессорных систем – Принстонская, или архитектура фон-Неймана и Гарвардская

В настоящее время существуют два типа архитектуры микропроцессорных систем – Принстонская, или архитектура фон-Неймана и Гарвардская - раздел Компьютеры, Материалы Лекций По Подготовке К Циклу Лабораторных Работ «Моделирование Микр...

Материалы лекций по подготовке к циклу лабораторных работ «Моделирование микропроцессора на базе кристалла Cyclone EP1C6T144C8».

Введение.

В настоящее время существуют два типа архитектуры микропроцессорных систем – Принстонская, или архитектура фон-Неймана и Гарвардская.

В 1945 г. американский математик Джон фон Нейман сформулировал основные принципы работы современных компьютеров. Им была предложена архитектура, получившая его имя (von Neumann architecture) и предполагающая хранение программ и данных в общей памяти (1946 г.).

Рисунок В.1. Структура МПС с фон-неймановской архитектурой.

Сегодня такая архитектура наиболее характерна для микропроцессоров, ориентированных на использование в компьютерах. Примером могут служить микропроцессоры семейства х86. Эти микропроцессоры относятся к CISC-процессорам(Complex Instruction Set Computer), т.е. процессорам с расширенным набором команд.

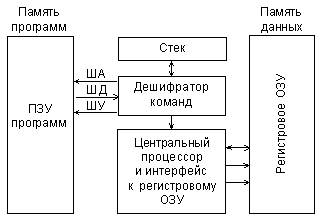

Архитектура, предполагающая раздельное использование памяти программ и данных, носит название гарвардской (Harvard architecture). Гарвардская архитектура позволяет центральному процессору работать одновременно как с памятью программ, так и с памятью данных, что существенно увеличивает производительность.

Рисунок В.2. Структура МПС с гарвардской архитектурой.

Данная архитектура ориентирована на использование RISC-процессоров (Reduce Instruction Set Computer), т.е. процессоров с ограниченным набором команд. В RISC-процессорах команды обращения к памяти данных выделены в отдельную группу. Регистры общего назначения (внутренняя память) RISC-процессоров, как правило, не имеют дополнительных специальных функций (кроме регистра нуля), их количество значительно превосходит внутреннюю память CISC-процессора.

Задание на моделирование

Для изучения основ функционирования микропроцессора предлагается построить самостоятельно модель простейшего RISC-процессора, выполняющего ограниченное количество команд. RISC-процессоры характеризуются раздельным обращением к областям памяти инструкций и данных. В настоящем цикле работ область памяти данных резервируется, но не рассматривается.

Процессор будет иметь исполнительный блок, содержащий 4 регистра. Регистры 8-разрядные. Регистр с младшим адресом, R0, всегда хранит « 0». Арифметико-логическое устройство, АЛУ, будет содержать только 8-разрядный сумматор. Выходы регистров подключаются к сумматору через мультиплексоры. Таким образом, проектируемый процессор может выполнять команды обмена с пространством памяти, команды внутренних пересылок и команды сложения. Как упоминалось ранее, обмен с пространством памяти пока не затрагиваем. Нас будут интересовать пересылки и сложение. Адресация таких действий может быть как регистровая ( источник и приемник адресуются по регистрам), так и непосредственная ( источник представлен 8-разрядным операндом в структуре команды). Формат команды 16 разрядов.

В этом формате выделяем следующие поля:

Р15 Р14 Р13 определяют код операции

1) 0 0 0 – запись операнда в память,

2) 0 0 1 – чтение операнда из памяти,

3) 0 1 0 – пересылка с непосредственной адресацией,

4) 0 1 1 – сложение с непосредственной адресацией,

5) 1 0 0 – пересылка с регистровой адресацией,

6) 1 0 1 – сложение с регистровой адресацией.

Первые 4 случая предполагают наличие операнда в структуре команды. Адресный операнд представим 4-разрядным, а операнд данных – 8-разрядным. Случаи 5 и 6 предполагают использование младшего байта команды под формирование кода.

Определим адресные поля источников и приемников. Команды с регистровой адресацией предполагают наличие двух источников: команда пересылки для RISC-процессора суммирует содержимое источника с нулем (R0) и записывает в приемник, для команды сложения второй источник может служить приемником. Выделяем для адресации разряды:

Р11 Р10 – адрес первого источника,

Р9 Р8 – адрес второго источника,

Р7 Р6 – адрес приемника.

Для случаев с непосредственной адресацией приемник адресуется по Р9 Р8. Для сложения с непосредственной адресацией непосредственный операнд по умолчанию должен записываться в R1, т.е. на разрядах Р11 Р10 в это случае должна присутствовать запись 01.

Проектируемый процессор будет выполнять следующий порядок команд:

MOV dat1, R1;

MOV dat2, R2;

ADD R1, R2;

MOV R2, R3

Введем значения непосредственных операндов. Пусть dat1=18, dat2=14. Запишем коды для этих команд. Неиспользуемые разряды заполним нулями.

| Р15 | Р14 | Р13 | Р12 | Р11 | Р10 | Р9 | Р8 | Р7 | Р6 | Р5 | Р4 | Р3 | Р2 | Р1 | Р0 |

Так как наш процессор будет выполнять лишь 4 команды, блок памяти инструкций для него можно представить в виде простейшего КЦУ, к выходу которого подключены два 8-разрядных регистра. На вход КЦУ поступают адреса от программного счетчика. Каждый адрес, таким образом, вызывает определенный программный код, который отображается в выходном буфере. Для настоящего цикла работ строим память на восемь 16-разрядных состояний. Минимальная единица информации для стандартной процессорной системы – байт, поэтому программный счетчик должен иметь 4 разряда. Управление блоком памяти производится тремя старшими разрядами, младший разряд подает тактовый сигнал на исполнительный блок. Структура полученного блока памяти инструкций представлена на рис.1. Программы для КЦУ и регистров – прогр.1 и прогр.2. Сигнал eninst=1 дает разрешение на обращение к памяти инструкций. Первая лабораторная работа настоящего цикла посвящена построению блока памяти и счетчика команд.

Записанный выше код инструкций содержит адреса направлений действий схемы (коды операций) и адреса устройств, непосредственно в этой операции участвующих (источников и преемников). Теперь нам необходимо построить управляющее устройство, формирующее сигналы управления на исполнительный блок. В состав этого устройства входят 4 дешифратора. Основной дешифратор получает код операции и управляет дешифраторами, определяющими местонахождение операндов, а также выводом операнда данных на внутреннюю шину данных, а адресного операнда на позиции, определяющие адрес в пространстве памяти данных. Управление формируется соответственно: для операнда данных – в случае команд переноса и сложения с непосредственной адресацией, для адресного операнда – в случае команд обращения к области памяти данных.

Так как команда пересылки MOV R(s),R(d) исполняется по принципу: R(d)<=R(s) + R(0), то для такой команды необходимы два источника: регистр нуля и регистр общего назначения. Кроме того, два источника могут понадобиться и для случая использования команды сложения двух операндов с занесением результата в третий регистр: ADD R(s1),R(s2),R(d). Поэтому договоримся, что два дешифратора определяют источники по разрядам кода Р11,Р10 и Р9,Р8; а один дешифратор определяет приемник по разрядам кода Р7,Р6. В случае, когда команда имеет только один операнд – источник, приемник определяется по разрядам Р9,Р8, т.е. с помощью дешифратора второго источника. Управление дешифратором первого источника получает активный уровень в случае исполнения команд: сложения (все адресации) и переноса с регистровой адресацией. Управление дешифратором второго источника получает активный уровень в случае исполнения команд сложения и переноса с регистровой адресацией. Управление дешифратором приемника получает активный уровень в случае исполнения команд сложения и переноса с любыми видами адресации.

Кроме того для команд сложения при любой адресации и переноса с регистровой адресацией блок управления формирует сигнал активизации АЛУ,

Полученная структура, включающая блок памяти, построенный ранее, представлена на рис.2. Программы для дешифраторов – прогр.3 и прогр.4. Построением блока устройства управления займемся на второй лабораторной работе.

Исполнительное устройство нашего процессора состоит из блока регистров и АЛУ. Построим блок регистров. Он включает в себя четыре 8-разрядных буферных регистра. Первый регистр всегда хранит «0», поэтому его входы данных не подключены к общей шине. В R0 может храниться только значение операнда источника. Следующие три регистра (R1, R2, R3) используются для общего назначения. Их входы данных подключены к общей шине, на которую может поступать как значение непосредственного операнда источника, так и содержимое выхода сумматора АЛУ. Простейшей развязкой этих сигналов в нашем случае может служить блок элементов 2ИЛИ. У каждого регистра буфер записи может быть включен только в том случае, если этот регистр служит приемником операнда (позиции приемник или второй источник). Полученная структура представлена на рис.3. Построению блока регистров посвящена третья лабораторная работа.

Второй блок решающего устройства – АЛУ. В нашем случае в него входит только 8-разрядный сумматор, два мультиплексора, собирающие выходы блока регистров, и триггер, хранящий состояние бита переноса. Полученная структура представлена на рис.4. Сумматор строится по программе – прогр.7, которая основана на прогр.5 и прогр.6. Прогр.5 описывает одноразрядный сумматор для нулевого разряда – без входа переноса, прогр.6 – одноразрядный сумматор, имеющий вход переноса. Построение блока АЛУ производится в процессе четвертой лабораторной работы.

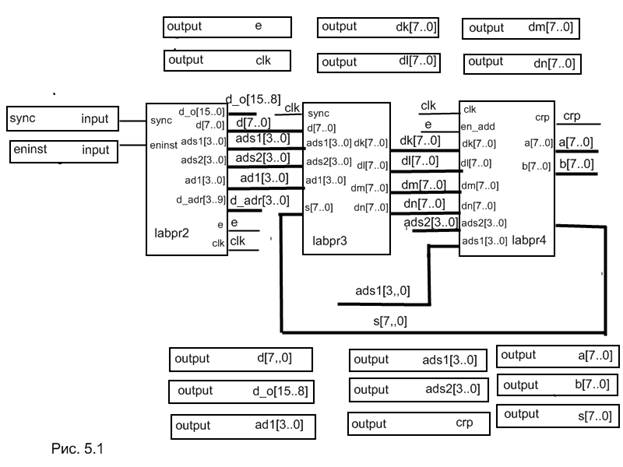

В пятой лабораторной работе полученные в процессе предыдущих работ модули объединяются согласно рис.5. Полученное устройство программируется в кристалл Cyclone EP1C6T144C6.

Все работы выполняются в пакете Quartus II. В нем уже выполнялись работы в предыдущем семестре, поэтому основные действия известны. Стоит привести лишь некоторые замечания, необходимые для проведения настоящих работ. Все проекты необходимо держать в одной общей папке. Каждый проект будет состоять из нескольких файлов. Перед компиляцией каждого файла необходимо установить его приоритет в данном проекте. Для этого необходимо включить навигатор проекта – первая иконка справа от окна названия проекта в верхнем меню. В открывшемся слева окне открыть список файлов проекта кнопкой File (средняя кнопка внизу открывшегося окна). Выбрать из списка необходимый файл и установить его приоритет (клик правой клавишей мыши, выбрать Set as Top Level Entity). Каждый проект необходимо оформлять как отдельный модуль (File –> Create/Update -> Create Symbol Files for Current File). При создании каждого нового проекта не забывайте в окне ADD FILES добавить уже созданные файлы, на основе которых будет строиться ваш проект. Если вы пропустили это на этапе формирования имени проекта, можете добавить через верхнее меню Project -> Add/Remove Files in Project

Описания лабораторных работ.

Лабораторная работа №1.

Формирование памяти инструкций.

Цель работы. Получение представления о формировании потока инструкций в RISC-процессоре. Ознакомление с программированием на VHDL. Постановка задачи. Необходимо построить схему блока, содержащую память…Задание на работу в лаборатории.

1. Открыть свою папку в пакете Quartus II и создать в ней проект для лабораторной работы №1.

2. Открыть VHDL-файл и записать в него текст прогр.1.1, ставя в соответствие каждому выделенному адресу сформированный код, записанный на лекции. Сохранить файл под именем raminst и установить его приоритет.

3. Откомпилировать файл программы и проверить с помощью временных диаграмм. На диаграммах установить интервалы: adr_i =20ns (20, 40 и 80 ns). Создать библиотечный модуль файла raminst.vhd.

4. Открыть файл графического редактора и, основываясь на работе в прошлом семестре, построить в нем синхронный 4-разрядный суммирующий счетчик. Сохранить файл под именем count и установить его приоритет.

5. Откомпилировать файл и проверить с помощью временных диаграмм. На диаграммах установить интервал sync =20ns. Создать библиотечный модуль файла count.bdf.

6. Открыть VHDL-файл и записать в него текст прогр.1.2 для 8-разрядного двухбуферного параллельного регистра. Сохранить файл под именем reg8 и установить его приоритет.

7. Откомпилировать файл и проверить с помощью временных диаграмм. На диаграммах установить интервал clk_i =20ns, ena и ctrl постоянно установить в «1», data_i сформировать произвольно. Создать библиотечный модуль файла reg8.vhd.

8. Открыть файл графического редактора и объединить в нем модули согласно рис.1.1. Сохранить файл под именем проекта, установить его приоритет.

9. Откомпилировать файл и проверить с помощью временных диаграмм. На диаграммах установить интервалы: sync =20ns, eninst=400ns. Продемонстрировать диаграммы преподавателю. Создать библиотечный модуль файла.

Отчет должен содержать: схему блока – рис.1.1, схему счетчика, программы для накопителя и регистров; временную диаграмму работы блока.

Прогр.1.1

use ieee.std_logic_1164.all; entity raminst isПрогр.1.2

use ieee.std_logic_1164.all; entity reg8 isЛабораторная работа №2.

Формирование устройства управления.

Постановка задачи. Необходимо построить устройство, посылающее сигналы управления на исполнительный блок. Из структуры кода команды следует. Что… Основной дешифратор управляет также выводом операнда данных на внутреннюю шину…Задание на работу в лаборатории.

1. Открыть свою папку в пакете Quartus II и создать в ней проект для лабораторной работы №2. Проекты всех лабораторных работ должны находиться в единой папке.

2. Открыть VHDL-файл и записать в него текст прогр.2.1 для дешифратора на 3 входа . Сохранить файл под именем dec и установить его приоритет.

3. Откомпилировать файл программы и проверить с помощью временных диаграмм. На диаграммах установить интервалы adr_i 20ns, 40ns и 80ns соответственно. Создать библиотечный модуль файла dec.vhd.

4. Открыть VHDL-файл и записать в него текст прогр.2.2 для дешифратора на 2 входа. Сохранить файл под именем dec1 и установить его приоритет.

5. Откомпилировать файл программы и проверить с помощью временных диаграмм. На диаграммах установить интервалы adr_i 20ns и 40ns соответственно. Создать библиотечный модуль файла dec1.vhd.

6. Открыть файл графического редактора и построить в нем схему рис.2.1, используя модули дешифраторов, модуль, полученный в результате работы № 1 и простую логику. Сохранить файл под именем проекта и установить его приоритет.

7. Откомпилировать файл и проверить с помощью временных диаграмм. На диаграммах установить интервалы: sync =20ns, eninst=400ns. Продемонстрировать диаграммы преподавателю. Создать библиотечный модуль файла.

Отчет должен содержать: схему блока – рис.2.1, программы для дешифраторов; временную диаграмму работы блока. Отчет представлять совместно с отчетом по лабораторной работе № 1.

Прогр.2.1

use ieee.std_logic_1164.all; entity dec is port(Прогр.2.2

use ieee.std_logic_1164.all; entity dec1 is port(Лабораторная работа № 3.

Формирование блока регистров.

Постановка задачи.Исполнительное устройство нашего процессора содержит два блока: блок регистров, где операнды временно хранятся для производства…Задание на работу в лаборатории.

1. Открыть свою папку в пакете Quartus II и создать в ней проект для лабораторной работы №3. Проекты всех лабораторных работ должны находиться в единой папке.

2. Открыть файл графического редактора и построить в нем схему по рис.3.1, используя модуль схемы 8-разрядного буферного регистра, созданный в лаб. работе № 1. Сохранить файл под именем проекта.

3. Откомпилировать файл и проверить с помощью временных диаграмм. На диаграммах установить интервалы: sync =40ns, ad1: ad1[1] =1 на интервале от 10 до 90ns, ad1[2] =1 на интервале от 90 до 170ns, data: data[1] =1 на интервале от 10 до 170ns, data[2] =1 на интервале от 90 до 170ns, data[3] =1 на интервале от 90 до 170ns, data[4] =1 на интервале от 10 до 90ns,s=0, ads1=0, ads2=0. Продемонстрировать диаграммы преподавателю. Создать библиотечный модуль файла.

Отчет должен содержать: схему блока – рис.3.1, временную диаграмму работы блока. Отчет представлять совместно с отчетом по лабораторным работам № 1 и №2.

Лабораторная работа № 4.

Формирование блока арифметико-логического устройства (АЛУ).

Постановка задачи.Последний из синтезируемых блоков – АЛУ. В нашем случае АЛУ состоит только из 8-разрядного сумматора. Программа, описывающая такой…Задание на работу в лаборатории.

1. Открыть свою папку в пакете Quartus II и создать в ней проект для лабораторной работы №4. Проекты всех лабораторных работ должны находиться в единой папке.

2. Открыть VHDL-файл и записать в него текст прогр.4.1 для одноразрядного сумматора без входа переноса. Сохранить файл под именем add1и установить его приоритет.

3. Откомпилировать файл add1. Открыть VHDL-файл и записать в него текст прогр.4.2 для одноразрядного сумматора. Сохранить файл под именем add11 и установить его приоритет.

4. Откомпилировать файл add11. Открыть VHDL-файл и записать в него текст прогр.4.3 для 8-разрядного сумматора. Сохранить файл под именем add8 и установить его приоритет.

5. Откомпилировать файл программы и проверить с помощью временных диаграмм. На диаграммах установить a=18 (a[1]=1, a[4]=1), b=14 (b[1]=1, b[2]=1, b[3]=1).

6. Открыть файл графического редактора и построить в нем схему рис.4.2, мультиплексор на 4 направления. Сохранить файл под именем mlt, установить его приоритет. Откомпилировать файл, создать библиотечный модуль.

7. Открыть файл графического редактора и построить в нем схему рис.4.3, блок из 8-ми мультиплексоров на 4 направления каждый. Сохранить файл под именем mult8, установить его приоритет. Откомпилировать файл, создать библиотечный модуль.

8. Открыть файл графического редактора и построить в нем схему рис.4.1, блок АЛУ, основанный на модулях мультиплексоров и сумматора. Сохранить файл под именем проекта, установить его приоритет.

9. Откомпилировать файл и проверить с помощью временных диаграмм. На диаграммах установить: clk=40ns, ads1[3..0] <=0010, ad2[3..0] <=0100, en_add=1, d1[7..0]<=00010010, d2[7..0] <=00001110, d0,d3 установить «0» во всех разрядах. Продемонстрировать диаграммы преподавателю. Создать библиотечный модуль файла.

Отчет должен содержать: схему блока – рис.4.1, программы для сумматора; временную диаграмму работы блока. Отчет представлять совместно с отчетами по лабораторным работам № 1, 2 и 3.

Прогр.4.1

library ieee;

use ieee.std_logic_1164.all;

entity add1 is

port(a1,b1:in BIT;c1,s1:out BIT);

end add1;

architecture struct_1 of add1 is

begin

s1<= ((a1 and (not b1)) or ((not a1) and b1));

c1<= a1 and b1;

end struct_1;

Прогр.4.2

library ieee;

use ieee.std_logic_1164.all;

entity add11 is

port(a2,b2,c1:in BIT;c2,s2:out BIT);

end add11;

architecture struct_1 of add11 is

begin

s2<=(a2 xor b2) xor c1;

c2<= (a2 and b2) or ((a2 xor b2)and c1);

end struct_1;

Прогр.4.3

use ieee.std_logic_1164.all; port(a,b:in bit_vector(7 downto 0);Лабораторная работа № 5.

Построение простейшего RISC-процессора.

Постановка задачи.У нас созданы основные модули общего проекта. Теперь необходимо аккуратно собрать их в единое целое, произвести верификацию…Задание на работу в лаборатории.

1. Открыть свою папку в пакете Quartus II и создать в ней проект для лабораторной работы №5. Проекты всех лабораторных работ должны находиться в единой папке.

2. Открыть файл графического редактора и построить в нем схему по рис.5.1, используя модули, созданные в предыдущих лабораторных работах. Сохранить файл под именем проекта.

3. Откомпилировать файл и проверить с помощью временных диаграмм. На диаграммах установить интервалы: sync =20ns, eninst=400ns. Продемонстрировать диаграммы преподавателю.

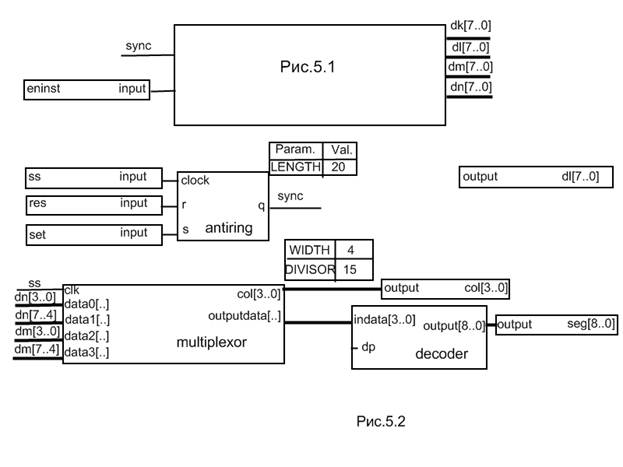

4. В разделе Материалы (afs – dcti.sut.ru – matherials – sk – 3kurs -…) найти файлы antiring, multiplexor, decoder, записать в проект и создать их библиотечные модули. Согласно рис.5.2 записать параметры модулей и включить их в схему.

5. Вызвать генератор разводки (Pin Planer) и, пользуясь распечаткой разводки и рис.5.2, произвести разводку внешней части кристалла. Полученную таблицу откомпилировать.

6. Вызвать программатор, убедиться в наличие всех настроек (файл, устройство, TAP, выбор режима) и запрограммировать кристалл. Продемонстрировать полученный результат преподавателю.

– Конец работы –

Используемые теги: настоящее, время, Существуют, Два, типа, архитектуры, микропроцессорных, систем, нстонская, архитектура, фон-, мана, Гарвардская0.148

Если Вам нужно дополнительный материал на эту тему, или Вы не нашли то, что искали, рекомендуем воспользоваться поиском по нашей базе работ: В настоящее время существуют два типа архитектуры микропроцессорных систем – Принстонская, или архитектура фон-Неймана и Гарвардская

Что будем делать с полученным материалом:

Если этот материал оказался полезным для Вас, Вы можете сохранить его на свою страничку в социальных сетях:

| Твитнуть |

Хотите получать на электронную почту самые свежие новости?

Новости и инфо для студентов