Аналіз паралельного інтерфейсу з DSP-процесорами: читання даних з АЦП, що під’єднаний до адресного простору пам’яті

Підключення АЦП або ЦАП через паралельний інтерфейс до DSP-процесора вимагає розуміння специфіки процесів читання/запису даних DSP-процесором з/в периферійних пристроїв при їх під’єднані до адресного простору пам'яті.

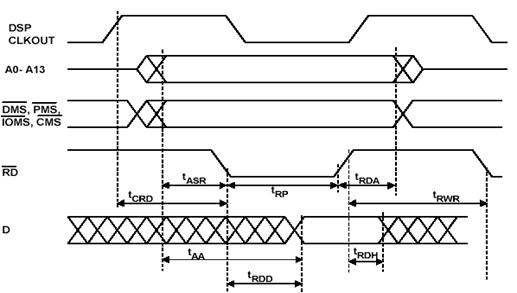

Спрощена блок-схема типового паралельного інтерфейсу DSP-процесора із зовнішнім АЦП наведена на рис. 4.1. Часова діаграма циклу читання для процесорів сімейства ADSP-21хх наведена на рис. 4.2. Вважається, що АЦП проводить вибірку з постійною частотою, яка задається зовнішнім тактовим генератором, асинхронно по відношенню до внутрішньої тактової синхронізації процесора. Використання окремого задаючого генератора для АЦП є перевагою, оскільки сигнал внутрішнього генератора процесора може мати високий рівень завад і фазовий шум (jitter), який в процесі аналого-цифрового перетворення веде до збільшення рівня шумів АЦП.

Тактовий імпульс задаючого генератора на вході "старт перетворення” (convert start) АЦП ініціює процес перетворення вхідних даних (крок N 1). По передньому фронту цього імпульсу внутрішня схема вибірки-зберігання АЦП перемикається з режиму вибірки в режим зберігання і таким чином починається процес перетворення. Після виконання перетворення на виході АЦП виставляється строб „перетворення виконано” (крок N 2). Коли цей сигнал поступає на вхід „запиту переривання DSP-процесора” (IRQ), починається процес читання даних з АЦП. Далі процесор виставляє на шині адресу периферійного пристрою, що ініціював запит на переривання (крок N 3). Одночасно процесор переводить в активний стан сигнал доступу до пам'яті (DMS) (крок N 4). Дві внутрішні шини адреси в процесорі ADSP-21хх (шина адреси пам'яті програм і шина адреси пам'яті даних) спільно використовують зовнішню шину адреси, а дві внутрішні шини даних (шина даних пам'яті програм і шина даних пам'яті даних) спільно використовують одну зовнішню шину даних. Сигнали „вибору пам'яті початкового завантаження” (BMS), „вибору пам'яті даних” (DMS), „вибору пам'яті програм” (PMS) і „вибору пам'яті пристроїв вводу-виводу” (IOMS) вказують, для якої пам'яті в даний момент використовуються зовнішні шини. Ці сигнали використовуються для зовнішньої дешифрації адреси (див.рис.4.1). Вихідний сигнал дешифратора адреси подається на вхід „chip select” вибору периферійного пристрою (крок N 5).

Сигнал читання пам'яті („memory read”, RD) виставляється через проміжок часу tASR після активації сигналу DMS (крок N 6). Щоб повністю використовувати перевагу високої швидкості DSP-процесора, сума часу затримки дешифрації адреси і часу включення периферійного пристрою після подачі сигналу вибору („chip select”) не повинна перевищувати час tASR. Сигнал RD залишається активним (низький логічний рівень) протягом часу tRP. Цей сигнал використовується для переведення в активний стан паралельного виходу даних периферійного пристрою (крок N 7). Сигнал RD звичайно підключається до відповідного виводу периферійного пристрою, що зветься сигналом „дозволу виходу” або „читання” („output enable” або „read”). Висхідний (задній) фронт сигналу RD використовується для введення даних з шини в DSP-процесор (крок N 8). Після появи висхідного фронту сигналу RD дані на шині повинні утримуватися периферійним пристроєм протягом часу tRDH, званого „часом утримання даних”. Для більшості процесорів сімейства ADSP-21хх цей час рівний нулю.

Рис.4.1.

Шина даних периферійного пристрою повинна підтримувати високоімпедансний Z-стан.

Час декодування адреси і час включення периферійного пристрою не повинен перевищувати час tASR установки процесором адреси і сигналу вибору пам'яті. Для здійснення доступу без режиму очікування, час від спадаючого (переднього) фронту сигналу RD до моменту достовірного встановлення даних не повинен перевищувати tRDD, інакше необхідно програмно забезпечити режим очікування або понизити частоту роботи процесора

На виході АЦП повинні підтримуватися достовірні дані протягом часу tRDH після висхідного (заднього) фронту сигналу читання RD.

Периферійний пристрій повинен працювати при якомога меншій тривалості строба tRP, інакше необхідно програмно забезпечити режим очікування або понизити частоту роботи процесора

Рис. 4.2.

Параметр tRDD визначає час, необхідний для доступу до даних периферійного пристрою. Якщо необхідний час доступу до периферійного пристрою більший, необхідно використовувати цикли очікування або зменшити тактову частоту процесора. Дані характеристики залежать від тактової частоти процесора DSP.

tCK - період тактового сигналу процесора; tASR - час установки процесором адреси і сигналу вибору пам'яті до спадаючого (переднього) фронту сигналу читання = 0.25·tCK; tRDD - час від спадаючого (переднього) фронту сигналу читання до моменту достовірної установки даних - 0.5·tCK + (число циклів очікування) × tCK (максимум); tRDH = час утримання даних після висхідного (заднього) фронту сигналу читання; tRP = тривалість імпульсу сигналу читання = 0.5·tCK + (число циклів очікування) × tCK (мінімум).

Є три спеціальні регістри для управління процесом очікування: для пам'яті початкового завантаження, для пам'яті програм і для пам'яті даних і простору вводу-виводу. Програміст може задати від 0 до 15 тактів очікування для кожного паралельного інтерфейсу пам'яті. Кожний такт очікування збільшує час доступу до зовнішньої пам'яті на величину, рівну по тривалості одному такту генератора тактових імпульсів процесора. В даному прикладі сигнали DMS і RD утримуються незмінними протягом додаткового часу, що визначається тривалістю тактів очікування.

Спрощена схема інтерфейсу між АЦП (типу AD7854/AD7854L) і DSP наведена на рис. 4.3. Як сигнал закінчення перетворення від AD7854/AD7854L використовується сигнал BUSY. Наведена конфігурація дозволяє DSP-процесору записувати дані в регістр управління паралельним інтерфейсом AD7854/AD7854L. Це необхідно для установки різних опцій в AD7854/AD7854L і виконання процесу калібрування. Проте в звичайному режимі читання даних з AD7854/AD7854L здійснюється відповідно до наведеного вище опису.