Аналіз паралельного інтерейсу з DSP-процесорами: запис даних в ЦАП, що під’єднаний до адресного простору пам’яті

Спрощена блок-схема інтерфейсу між DSP-процесором і наприклад ЦАП) наведена на рис. 4.4. Діаграми циклу запису в пам'ять для сімейства ADSP-21xx наведені на рис.6.

В системах реального часу ЦАП здійснюють подвійну буферизацію даних і функціонують безперервно з постійною тактовою частотою.

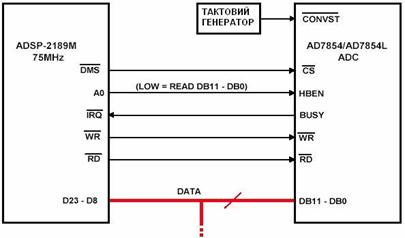

Рис. 4.3.

Рис. 4.4.

Рис. 4.5.

Процес запису ініціюється ЦАП за допомогою встановлення сигналу запиту переривання процесора, який вказує, що периферійний пристрій готовий до прийому нових даних (крок N 1). Далі процесор виставляє адресу ЦАП на адресній шині (крок N 2) і переводить у активний стан сигнал DMS (крок N 3). Це приводить до того, що дешифратор адреси видає сигнал вибору (chip select) на периферійний пристрій (крок N 5). Після спадаючого фронту сигналу DMS через проміжок часу tASW процесор переводить в активний нульовий стан сигнал запису WR (крок N 4). Тривалість імпульсу WR складає tWP нс. Дані поступають на шину даних (D) і утримуються протягом часу tDW, до переходу сигналу WR в неактивний одиничний стан (крок N 6). Висхідний фронт сигналу WR використовується для фіксації присутніх на шині даних (D) в зовнішню паралельну пам'ять (крок N 7). Дані на шині залишаються достовірними ще протягом часу tDH після проходження позитивного фронту сигналу WR.

tCK - період тактового сигналу процесора; tASW - час установки процесором адреси і сигналу вибору пам'яті до спадаючого фронту сигналу запису - 0.25·tCK; tDW - час від моменту установки даних до висхідного фронту сигналу запису - 0.5·tCK + (число циклів очікування) × tCK; tDH - час затримки даних після висхідного фронту сигналу запису - 0.25·tCK; tWP - тривалість імпульсу сигналу запису WR - 0.5·tCK + (число циклів очікування) × tCK (мінімум);

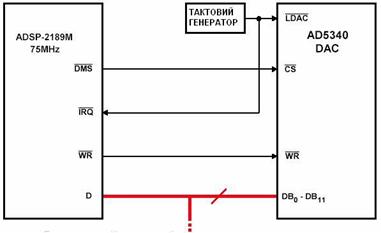

Спрощена схема інтерфейсу між ADSP-2189M і ЦАП AD5340 наведена на рис. 4.6.

Примітки: Використовується 2 програмних цикли очікування

Тактові імпульси можна одержувати від DSP - процесора

Рис. 4.6.