Реалізація алгоритмів опрацювання сигналів та зображень на нейропроцесорах

Нейрокомпьютер - це обчислювальна система з MSІMD архітектурою, тобто з паралельними потоками однакових команд і множинним потоком даних. На сьогодні можна виділити три основних напрямки розвитку обчислювальних систем з масовим паралелізмом (ОСМП):

| № | Найменування напрямку | Опис |

| ОСМП на базі каскадного з'єднання універсальних SІSD, SІMD, MІSD мікропроцесорів. | Елементна база - універсальні RІSC чи CІSC процесори: Іntel, AMD, Sparc, Alpha, Power PC, MІPS і т.п. | |

| На базі процесорів з розпаралелюванням на апаратному рівні. | Елементна база - DSP процесори: TMS, ADSP, Motorola, ПЛИС. | |

| ОСМП на спеціалізованій елементній базі | Елементна база від спеціалізованих однобітових процесорів до нейрочіпів. |

Нейромережеві системи, реалізовані на апаратних платформах першого напрямку (нехай і мультипроцесорних) будемо відносити до нейроемуляторів - тобто систем, що реалізують типові нейрооперації (зважене підсумовування і нелінійне перетворення) на програмному рівні. Нейромережеві системи, реалізовані на апаратних платформах другого і третього напрямку у виді плат розширення стандартних обчислювальних систем (1-го напрямку) - будемо називати нейроприскорювачами і системи, реалізовані на апаратній платформі третього напрямку у виді функціонально закінчених обчислювальних пристроїв, варто відносити до нейрокомп’ютерів (всі операції виконуються в нейромережевому логічному базисі). Нейроприскорювачі можна розділити на два класи "віртуальні" (вставляються в слот розширення стандартного РС) і "зовнішні"(щоз'єднуються з керуючою Host ЕОМ по конкретному інтерфейсі чи шині). Нейро засоби проектуються на базі ПЛІС, каскадного з’єднання DSP-процесорів типу ADSP2106x, TMS320C4x,8x, DSP96002 і ін. , спеціалізованих процесморів, наприклад, Л1879ВМ1 (NM6403)

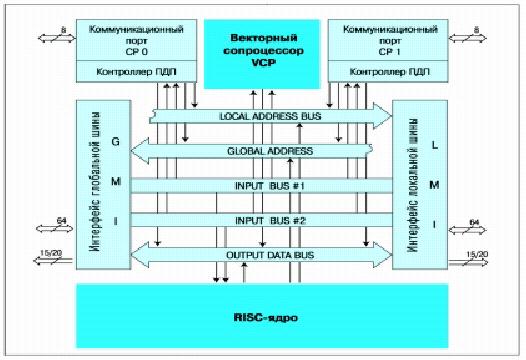

Процесор Л1879ВМ1 є високопродуктивним спеціалізованим мікропроцесором, що об’єднює в собі риси двох сучасних архітектур: VLIW (Very Long Instruction Word) і SIMD (Single Instruction Multiple Data) (рис. 7.1). Основні обчислювальні вузли процесора - керуюче RISC-ядро і векторний співпроцесор. RISC-ядро – це центральний процесорний вузол, що виконує всі основні функції по керуванню роботою кристала. Крім того, RISC-процесор робить арифметико-логічні і операції зсуву над 32-розрядними скалярними даними і формує 32-розрядні адреси команд і даних при звертаннях до зовнішньої пам'яті. Довжина команди - 32 і 64 розряди (звичайно в команді виконуються дві операції). Процесор реалізує п’ятиступінчатий 32-розрядний конвеєр. Адресний простір - 16 Гбайт, два адресних генератори, вісім регістрів загального призначення і вісім адресних регістрів. Будь-яка інструкція виконується за один такт. Векторний співпроцесор призначений для арифметичних і логічних операцій над 64-розрядними скалярними даними програмувальної розрядності. Обмін даними між основними вузлами процесора відбувається по трьох внутрішніх шинах, двох вхідним і одній вихідній.

Рис. 7.1.Архітектура процесора NM6403

GMI і LMI-два однакових блоки програмувального інтерфейсу з локальною і глобальною 64-розрядними зовнішніми шинами. До кожної з них може бути підключена зовнішня пам'ять, що містить до 231 32-розрядних комірок. Обмін даними з зовнішньою пам'яттю здійснюється як 32-, так і 64-розрядними словами (NM6403 одночасно вибирає дві сусідні комірки пам'яті). Кожен блок програмувального інтерфейсу дозволяє працювати з двома банками зовнішньої пам'яті різного обсягу, типу (DRAM, SRAM, Flash ROM, EDO DRAM і т.д.) і швидкодії без додаткового устаткування. Передбачено апаратну підтримку режиму розподіленої пам'яті для різних мультипроцесорних конфігурацій зовнішніх шин.

СР1 і СР2- ідентичні комунікаційні порти, що забезпечують інформаційний обмін по двонаправленій восьмиразрядной шині. Вони призначені для побудови високопродуктивних мультипроцесорних систем і цілком сумісні з комунікаційними портами процесора ТМ320C4x. Кожен комунікаційний порт має вбудований контролер прямого доступу до пам'яті (ПДП, DMA), що дозволяє обмінюватися 64-розрядними даними з пам'яттю на зовнішніх шинах.