рефераты конспекты курсовые дипломные лекции шпоры

- Раздел Высокие технологии

- /

- Вид работы: Лекции

- /

- Курс лекций по предмету Микропроцессоры и микропроцессорные системы специальности 230101

Реферат Курсовая Конспект

Курс лекций по предмету Микропроцессоры и микропроцессорные системы специальности 230101

Курс лекций по предмету Микропроцессоры и микропроцессорные системы специальности 230101 - Лекция, раздел Высокие технологии, Курс Лекций По Предмету «Микропроцессоры И Микропроцесс...

Курс лекций по предмету «Микропроцессоры и микропроцессорные системы» специальности 230101

Занятие 1.(1)

Введение.

В этой лекции кратко приведена история развития информатики, рассматриваются принципы построения, поколения и классификация ЭВМ и принципы их построения, а также основные модели ПЭВМ.

Цель: познакомить учащихся с историей развития информатики, сформировать знания о принципах построения ЭВМ, и умения определять, к какому классу ЭВМ относятся современные вычислительные машины.

История развития вычислительной техники

Однако основы информационной теории и техники как таковой были заложены в XVII веке Шиккардом, Паскалем и Лейбницем. Вот они - этапы большого… 1623 г. - В. Шиккард, профессор Тюбингенского университета предложил агрегат,… 1642 г. - Блез Паскаль продемонстрировал в Люксембургском дворце машину, которая могла складывать и вычитать.Принципы построения ЭВМ

Кроме машин фон Неймана существуют потоковые и редукционные ЭВМ. Дж. Деннис в 1967 г. сформулировал принципы построения потоковых ЭВМ - должны…Поколения ЭВМ

Классификация ЭВМ

Одна из общепринятых классификаций ЭВМ приведена Б.С. Богумирским. Нам она представляется приемлемой и на сегодняшний день.

- Большие ЭВМ (mainframe) IBM 360/370, ЕС ЭВМ, ES/9000, IBM S/390.

- Супер-ЭВМ (Cray J90, Convex C38XX, IBM SP2, SGI POWER CHALLENGE, системы MPP, Электроника СС-100, Эльбрус-3).

- Мини-ЭВМ (PDP-11, VAX, СМ ЭВМ).

- Микро-ЭВМ:

- АРМ;

- встроенные;

- ПЭВМ.

С точки зрения взаимодействия команд и данных, интересна классификация ЭВМ по Флинну:

- ОКОД (SISD) - "одиночный поток команд, одиночный поток данных". Традиционная архитектура фон Неймана + КЭШ + память + конвейеризация.

- ОКМД (SIMD) - "одиночный поток команд, множественный поток данных".

- МКМД (MIMD) - "множественный поток команд, множественный поток данных", мультипроцессорные системы (несколько устройств управления и АЛУ).

Основные модели ПЭВМ

Основные модели ПЭВМ, представленные на рынке:

- ЭВМ фирмы IBM и их аналоги. Характерен принцип открытости архитектуры.

- ЭВМ фирмы Apple собираются на базе микропроцессоров фирмы Motorola, представлены двумя семействами: Apple и Macintosh. Основное отличие от ЭВМ фирмы Intel -замкнутость архитектуры.

- ЭВМ независимых фирм производителей.

Назначение и типы микропроцессоров.

Микропроцессор (МП) - это программно управляемое устройство, которое предназначено для обработки цифровой информации и управления процессом этой обработки и выполнено в виде одной или нескольких больших интегральных схем (БИС).

Микропроцессорная система (МПС) представляет собой функционально законченное изделие, состоящее из одного или нескольких устройств, основу которой составляет микропроцессор.

Классификация микропроцессоров

Универсальные микропроцессоры предназначены для решения задач цифровой обработки различного типа информации от инженерных расчетов до работы с базами данных, не связанных жесткими ограничениями на время выполнения задания. Этот класс микропроцессоров наиболее широко известен. К нему относятся такие известные микропроцессоры, как МП ряда Pentium фирмы Intel и МП семейства Athlon фирмы AMD.

Характеристики универсальных микропроцессоров:

• разрядность: определяется максимальной разрядностью целочисленных данных, обрабатываемых за 1 такт, то есть фактически разрядностью арифметико-логического устройства (АЛУ);

• виды и форматы обрабатываемых данных;

• система команд, режимы адресации операндов;

• емкость прямоадресуемой оперативной памяти: определяется разрядностью шины адреса;

• частота внешней синхронизации.

• производительность: определяется с помощью специальных тестов, при этом совокупность тестов подбирается таким образом, чтобы они по возможности покрывали различные характеристики микроархитектуры процессоров, влияющие на производительность.

Однокристальные микроконтроллеры (ОМК или просто МК) предназначены для использования в системах промышленной и бытовой автоматики. Они представляют собой большие интегральные схемы, которые включают в себя все устройства, необходимые для реализации цифровой системы управления минимальной конфигурации: процессор (как правило, целочисленный), ЗУ команд, ЗУ данных, генератор тактовых сигналов, программируемые устройства для связи с внешней средой (контроллер прерывания, таймеры-счетчики, разнообразные порты ввода/вывода), иногда аналого-цифровые и цифро-аналоговые преобразователи и т. д. В некоторых источниках этот класс микропроцессоров называется однокристальными микро-ЭВМ (ОМЭВМ).

Секционированные микропроцессоры (другие названия: микропрограммируемые и разрядно-модульные) - это микропроцессоры, предназначенные для построения специализированных процессоров. Они представляют собой микропроцессорные секции относительно небольшой (от 2 до 16) разрядности с пользовательским доступом к микропрограммному уровню управления и средствами для объединения нескольких секций.

Процессоры цифровой обработки сигналов, или цифровые сигнальные процессоры, представляют собой бурно развивающийся класс микропроцессоров, предназначенных для решения задач цифровой обработки сигналов - обработки звуковых сигналов, изображений, распознавания образов и т. д. Они включают в себя многие черты однокристальных микро контроллеров: гарвардскую архитектуру, встроенную память команд и данных, развитые возможности работы с внешними устройствами. В то же время в них присутствуют черты и универсальных МП, особенно с RISC-архитектурой: конвейерная организация работы, программные и аппаратные средства для выполнения операций с плавающей запятой, аппаратная поддержка сложных специализированных вычислений, особенно умножения.

Занятие 2 (2)

Архитектура микропроцессорных систем

- одношинная, или принстонская, фон-неймановская архитектура Соответственно, в составе системы в этом случае присутствует одна общая…Упрощенная структура микропроцессора

Для выполнения команд в структуру процессора входят: - внутренние регистры, - арифметико-логическое устройство (АЛУ, ALU — Arithmetic Logic Unit) ,Арифметико-логические устройства

Структурная схема АЛУ сложения/вычитания чисел с фиксированной запятой.

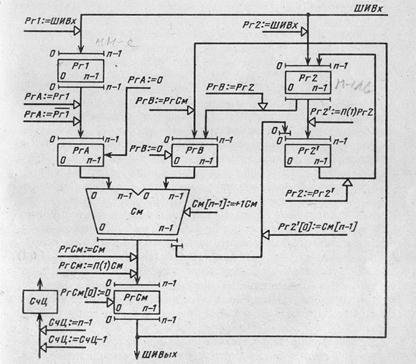

В АЛУ сложения и вычитания с фиксированной точкой оба операнда поступают с шины входа: первый операнд в Рг1, второй в РгВ при поступление на вход управляющих сигналов прием Рг 1(ПрРг1) и приём РгВ(Пр РгВ).

Если знак первого числа положительный, то осуществляется передача первого операнда из Рг1 в РгА в прямом коде (ПрРгАП). Если знак отрицательный, то в инверсном ( приём (ПрРгАИ).

С выходом регистров А и В операнды поступают на сумматор, если знак первого операнда был отрицательный, то к младшему разряду суммы прибавляется 1(единица).

Сумма поступает на регистр сумматора ( Пр Рг СМ).

По результату выполнения операции форматируются признаки результата:

00- если результат равен “0”

01- если результат отрицательный

10 - если результат положительный

11 - если происходит переполнение разрядной сетки

Для формирования признака результата анализируются следующие данные:

См [1-7]; перенос См в знаковый разряд Пн См [1], перенос См из знакового разряда Пн См [0], См [0] - знаковый разряд.

Признак 00 формируется, если логическое произведение инверсных значений всех разрядов результата равен единице.

Признак результата 01 формируется по формуле: См[0] И ( НЕ (Пн См[1] М2 Пн См [0])

Признак результата 10 формируется по формуле: НЕ (См[0]) И ( НЕ (Пн См[1] М2 Пн См [0]))

Признак результата 11 формируется по формуле: Пн См [1] М2 Пн См [0]

Микропрограмма сложения

| Микрокоманда | Операция |

| ПрРг1 | Рг1:=ШиВх |

| ПрРгВ | РгВ :=ШиВх |

| ПрРгА Пр | РгА:=Рг1 |

| См:=РгА+РгВ | |

| ПрРгСм | РгСм:=См |

| ПрШиВых | ШиВых:=РгСм |

Микропрограмма вычитания

| Микрокоманда | Операция |

| ПрРг1 | Рг1:=ШиВх |

| ПрРгВ | РгВ:=ШиВх |

| ПрРгА И | РгА:= НЕ(Рг1) |

| См:=РгА+РгВ+1 | |

| ПрРгСм | РгСм:=См |

| ПрШиВых | ШиВых:=РгСм |

Занятие 4 (4)

Структурная схема АЛУ умножения чисел с фиксированной запятой.

Операция умножения сводится к сложению и сдвигу частичных произведений вправо на один разряд. Знак результата определяется путем сложения по модулю два знаков операндов. Формат произведения в два раза больше, чем множимых.

При выполнение умножения выполняется логический сдвиг, т.е. сдвиг без знаковых разрядов.

Для проверки разряда множителя необходимо его сдвигать.

Умножение осуществляется по циклам, количество циклов равно количеству разрядов операндов. Для этого в схеме предусмотрен счётчик циклов (Сч.Ц.).

На Рг1 с шины входа поступает множимое, на Рг2 множитель. Их формат одинаковый.

Множитель из Рг1 в РгА может передаваться без изменений, если младший разряд множителя равен 1. Если он равен 0 , то множимое в РгА не передаётся. Анализ младшего разряда множителя осуществляется с помощью конъюнктура.

Между Рг2 и Рг2' существует косая передача со сдвигом вправо на один разряд. Из Рг2' осуществляется прямая перезапись сдвинутого множителя. В освобождающейся, при сдвиге, старший разряд в Рг2' записывается младший разряд сумматора. Т.к. в процессе умножения необходим сдвиг частичных произведений, то между сумматором и Рг См существует так же косая передача вправо на один разряд.

Умножение заканчивается , когда Сч.Ц равен нулю. Результат умножения записывается - старшая часть в Рг См, а младшая часть в РгВ.

Микропрограмма умножения

| Рг 1, РгА | РгВ, См, РгСм | Рг2, Рг2’ | Сч Ц |

| Рг1 : = 1100 РгА:=0000 | РгВ:=0000 См:=0000 РгСм:=0000 | Р г2: = 1010 Рг2’:=0000 | СчЦ:=4 |

| РгА:=Рг1=0000 | См:=РгА+РгВ=0000+0000= РгСм:=П[ 1 ]См=0000 РгВ: = РгСм=0000 | Рг2[n-1]:=0 Рг2’ [0]: = См[п-1] = 0 Рг2’:=П[1]Рг2=0101 Рг2:=Рг2’=О101 | СчЦ =3 |

| РгА:=Рг1=1100 | См:=РгА+РгВ=1100 + 0000= РгСм:=П[ 1 ]См=0110 РгВ:=РгСм=0 1 10 | Рг2[п-1]: = 1 Рг2’[0]:=См[п-1] = 0 Рг2’:=П[1]Рг2=0010 Рг2:=Рг2’ = 0010 | СчЦ:=2 |

| РгА:=Рг1=0000 | См: = РгА+РгВ=0000+0110= РгСм:=П[ 1]См=0011 РгВ :=РгСм=001 1 | Рг2[п-1]:=0 Рг2’[0]:=См[п-1]=0 Рг2’:=П[ 1 ] Р г2 = 0001 Рг2:=Рг2’ = 0001 | СчЦ:= 1 |

| РгА:=Рг1=1100 | См: = РгА+РгВ=1100+0011 = 1111 РгСм:=П[1]См=0111 РгВ:=РгСм=0111 | Рг2[п-1]: = 1 Рг2’[0]:=См[п-1]=1 Рг2’:=П[1]Рг2= 1000 Рг2: = Рг2’= 1 000 | СчЦ:=0 |

| Выдача результата: РгВ:=Рг2=1000 ШИВых:=РгВ = 0111 - старшая половина ШИВых:=РгСм=1000 - младшая половина |

Занятие 6 (6)

Структурная схема АЛУ деления чисел с фиксированной запятой.

Деление в ЭВМ обычно сводится к выполнению последовательности вычитаний делителя сначала из делимого, а затем из образующихся в процессе деления частичных остатков и сдвига частичных остатков.

1. Деление с неподвижным делимым и сдвигаемым вправо делителем. Этот способ деления основан на прямом копировании действий при ручном делении.

Недостатком такого АЛУ является двойная длина сумматора и его регистров.

2. Деление с неподвижным делителем и сдвигаемым влево делимым.

Этот способ позволяет строить АЛУ с сумматором одинарной длины. Здесь неподвижный делитель К хранится в РгУ, а делимое X, сдвигаемое влево относительно У, находится в двух регистрах: старшие разряды X — в Рг1Х, а младшие — в Рг2Х. Деление начинается со сдвига влево делимого X путем косой передачи его в РгСм и РгЗХ и соответствующих прямых передач в Рг1Х и Рг2Х. Далее на вход сумматора подается сдвинутое влево делимое, образуется частичный остаток путем подсуммирования дополнительного кода делителя, и очередная цифра частного заносится в освободившийся при сдвиге X разряд Рг2Х.

Арифметическо-логическое устройство рассмотренного типа широко используется для деления

Алгоритм деления с неподвижным делителем с восстановлением остатка:

1. Берутся модули от делимого и делителя.

2. Исходное значение частичного остатка полагается равным старшим разрядам делимого.

3. Частичный остаток удваивается путем сдвига на один разряд влево, при этом в освобождающийся при сдвиге младший разряд частичного остатка заносится очередная цифра делимого.

4. Из сдвинутого частичного остатка вычитается делитель и анализируется знак результата вычитания.

5. Очередная цифра модуля частного равна 1, если результат вычитания положителен, и 0, если отрицателен. В последнем случае значение остатка восстанавливается до того, которое было до вычитания.

6. Пункты 3 — 5 последовательно выполняются для получения всех цифр модуля частного.

7. Знак частного плюс, если знаки делимого и делителя одинаковы, и минус в противном случае.

Рассмотренный метод деления носит название деления с восстановлением остатка. Недостатком этого метода является необходимость введения специального такта для восстановления остатка.

Алгоритм деления с неподвижным делителем без восстановления остатка:

Пункты 1 — 3 совпадают с аналогичными пунктами алгоритма деления с восстановлением остатка.

4. Из сдвинутого частичного остатка вычитается делитель, если остаток положителен, и к сдвинутому частичному остатку прибавляется делитель, если остаток отрицателен.

5. Очередная цифра модуля частного равна 1, если результат вычитания положителен, и 0, если отрицателен.

Пункты 6, 7 совпадают с аналогичными пунктами предыдущего алгоритма.

Можно показать, что частичные остатки после выполнения сложения при делении без восстановления остатка получаются такими же, как и после сдвига восстановленного остатка при делении с восстановлением остатка.

Занятие (7)

Многофункциональное АЛУ (рис.8)

В многофункциональных АЛУ операции над числами с фиксированной и плавающей запятой, десятичными числами; и алфавитно-цифровыми полями выполняются в основном одними и теми же схемами, коммутируемыми соответствующим образом. На рис. 8 приведена схема многофункционального АЛУ для выполнения совокупности рассматривавшихся арифметических и логических операций. В данной схеме в качестве отдельных фрагментов можно выделить описанные выше АЛУ, при этом для сокращения общего числа связей некоторые связи следует удалить (фактически заменить другими). Так, например, при сложении чисел с фиксированной запятой в отличие от АЛУ в рассматриваемой схеме загрузка РгВ происходит не от ШИВх, а от Рг2 ввиду того, что связь от ШИВх к Рг2 и далее к РгВ должна существовать из-за необходимости реализации умножения. Сумма частичных произведений заносится в РгВ не непосредственно из РгСм, а через РгЗ, так как загрузка РгЗ необходима при выполнении сложения чисел с плавающей запятой и т. п.

Операции двоично-десятичной арифметики в данном АЛУ производятся при помощи двоично-десятичного сумматора СмДес и побайтной организации обработки.

При выполнении операций над числами с плавающей запятой используются двоичный сумматор См и схема СОЛО. При сложении (вычитании) чисел с плавающей запятой первое слагаемой (уменьшаемое) поступает на входной регистр Рг1, второе (вычитаемое) — на входной регистр РгЗ. Знаки слагаемых хранятся в триггерах знаков ТгЗн! и ТгЗн2. Смещенные поряд-

ки слагаемых пересылаются в регистры РгС и РгД. Схема СОЛО применяется для сравнения и выравнивания порядков слагаемых. Сумматор См, его входные регистры РгА и РгВ и выходной регистр РгСм используются при сложении (вычитании) мантисс, а также при передаче мантисс со сдвигом в процедурах выравнивания порядков и нормализации результата.

ки слагаемых пересылаются в регистры РгС и РгД. Схема СОЛО применяется для сравнения и выравнивания порядков слагаемых. Сумматор См, его входные регистры РгА и РгВ и выходной регистр РгСм используются при сложении (вычитании) мантисс, а также при передаче мантисс со сдвигом в процедурах выравнивания порядков и нормализации результата.

Выравнивание порядков осуществляется следующим образом. Смещенный порядок числа X из РгЗ передается в регистр РгД и в выполняющий роль РгСОЛО счетчик РгСч1, соединенный с выходом СОЛО. Затем в РгС передается смещенный порядок числа У.

После этого начинается сравнение порядков чисел I и Уна СОЛО и сдвиг мантиссы числа с меньшим порядком вправо, при этом значение смещенного порядка вменяется до тех пор, пока он не станет равным смещенному порядку X. Порядок 2 берется равным большему порядку слагаемых.

Чтобы не делать лишних сдвигов мантиссы, превратившейся в процессе выравнивания порядка в 0, на счетчике циклов СчЦ фиксируется предельное число сдвигов, равное числу шестнадцатиричных цифр мантиссы:

СчЦ: = 6.

При выполнении сдвига на один шестнадцатиричный разряд содержимое СчЦ уменьшается на 1. При СчЦ = 0 сдвиги прекращаются и в качестве результата берется большее слагаемое.

После выравнивания порядков осуществляется сложение мантисс и (при необходимости) нормализация результата.

При умножении чисел с плавающей запятой используются: сумматор См; регистр Рг1 для хранения множимого; регистры Рг2 и РгТ для приема и сдвига множителя в процессе умножения мантисс; регистр РгА, используемый для передачи на сумматор смещенного порядка множимого при суммировании порядков и для передачи на сумматор мантиссы множимого при умножении мантисс; регистр РгВ, служащий для передачи на сумматор смещенного порядка множителя при суммировании порядков и для хранения текущей суммы частичных произведений при умножении мантисс; выходной регистр сумматора РгСм, фиксирующий результаты суммирований; счетчик РгСч1, хранящий смещенный порядок произведения; триггеры знаков сомножителей ТгЗн1 и ТгЗн2.

При выполнении деления чисел с плавающей запятой используются: сумматор См; регистры Рг и Рг2 для приема соответственно делителя и делимого; регистры РгА и РгВ для хранения смещенных порядков делителя и делимого и для хранения мантиссы делителя и частичного остатка при получении мантиссы частного; счетчик Сч1 для хранения смещенного порядка частного; регистры Рг2 и Рг2' для хранения цифровых разрядов мантиссы частного; триггеры знаков делимого и делителя ТгЗн1 и ТгЗн2.

Занятие 8(8)

Шинная структура МПС

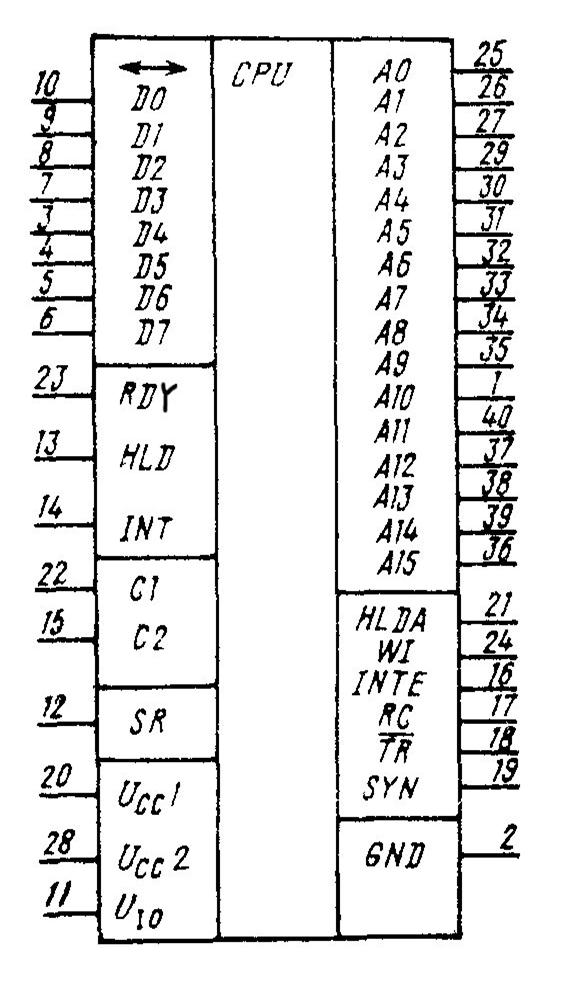

При классической структуре связей все сигналы и коды между устройствами…Типичная структура микропроцессорной системы

Она включает в себя три основных типа устройств: процессор; память, включающую оперативную память (ОЗУ, RAM — Random Access Memory) и … Все устройства микропроцессорной системы объединяются общей системной шиной… Системная магистраль включает в себя четыре основные шины нижнего уровня: шина адреса (Address Bus); шина данных…Состав блока регистров микропроцессора.

- основные функциональные регистры; - регистры процессора с плавающей точкой; - системные регистры;Устройство управления микропроцессора.

Различают 2 типа организации схем управления:

- управление с жесткой логикой (схемное управление), характеризуется высоким быстродействием, так как операция выполняется за один такт и высокими аппаратурными затратами

- управление с гибкой логикой (микропрограммное управление) характеризуется низкими аппартурными затратами и быстродействием

Интерфейсы ввода-вывода.

осуществляют электрическое согласование параметров внутренней магистрали с сигналами внешних магистралей, формирование необходимых сигналов на внешнюю магистраль и прием сигналов извне.

– Конец работы –

Используемые теги: курс, лекций, предмету, Микропроцессоры, Микропроцессорные, системы, специальности, 2301010.112

Если Вам нужно дополнительный материал на эту тему, или Вы не нашли то, что искали, рекомендуем воспользоваться поиском по нашей базе работ: Курс лекций по предмету Микропроцессоры и микропроцессорные системы специальности 230101

Что будем делать с полученным материалом:

Если этот материал оказался полезным для Вас, Вы можете сохранить его на свою страничку в социальных сетях:

| Твитнуть |

Хотите получать на электронную почту самые свежие новости?

Новости и инфо для студентов