рефераты конспекты курсовые дипломные лекции шпоры

- Раздел Высокие технологии

- /

- АРХИТЕКТУРА МИКРОКОНТРОЛЛЕРА

Реферат Курсовая Конспект

АРХИТЕКТУРА МИКРОКОНТРОЛЛЕРА

АРХИТЕКТУРА МИКРОКОНТРОЛЛЕРА - раздел Высокие технологии, Введение С...

ВВЕДЕНИЕ

Создание фирмой Intel в 1971 году первой программируемой электронной схемы на одном кристалле явилось началом эпохи микропроцессорной техники. Объединив в себе достижения вычислительной техники и микроэлектроники, микропроцессорные системы стали удобным общепринятым инструментом для построения самых различных систем автоматики.

За 30 лет своего бурного развития микропроцессорные системы прошли путь от специализированных комплектов интегральных схем к сложным однокристальным микроконтроллерам, имеющим в своем составе целый набор самых различных программируемых элементов. Их разработкой занимаются практически все крупнейшие мировые производители компьютеров, бытовой техники, промышленных систем и электронных компонентов - всем известные: INTEL, AMD, ATMEL, MICROCHIP, MITSUBISHI, MOTOROLA, ANALOG DEVICE, NATIONAL SEMICONDUCTOR, SIEMENS, TEXAS INSTRUMENT, ZILOG и др. Они выпускаются сейчас, как и все остальные микросхемы, миллионными партиями, а стоимость одного микроконтроллера, как правило, составляет всего несколько долларов.

В условиях существующей в области микроэлектроники жесткой конкуренции каждый производитель выбирает свою модель развития, предлагая множество новых технических и технологических решений. При этом не успевают устояться условные обозначения и терминология, появляется множество архитектур и языков программирования, что существенно усложняет изучение и освоение этой техники. В нашей стране ситуация усугубляется языковым барьером, вся основная терминология в этой области техники имеет английскую аббревиатуру.

Вместе с тем, принципы построения микропроцессорных систем, несмотря на множество направлений развития, не подвергаются существенной переработке. Заложенные в 70-х годах, при всем многообразии изделий, они без значительных изменений сохраняются и до настоящего времени. По этой причине изучение микропроцессорной техники возможно, и всегда строится, на конкретных примерах какой либо одной архитектуры. Именно по этому принципу строятся учебные курсы, предлагаемые в настоящее время ведущими университетами и учебными центрами. В качестве примеров обычно рассматриваются микроконтроллеры Intel, Motorola, Zilog, Microchip [1-5].

Все основные понятия микропроцессорной техники в пособии рассмотрены на примерах современных AVR-микроконтроллеров фирмы Atmel. Этот выбор обусловлен целым рядом факторов, таких как распространенность микроконтроллеров в России, доступность технической информации, наличие свободно распространяемых программных и сравнительно недорогих аппаратных средств поддержки проектирования. Использованные при написании пособия оригинальные материалы можно найти на сайте www.atmel.ru.

АРХИТЕКТУРА МИКРОКОНТРОЛЛЕРА

Контроллером в технике регулирования считается управляющее устройство, осуществляющее регулирующие или контролирующие функции в системе. Контроллер,… Типовая структура микроконтроллера изображена на рис. 1.1. Микроконтроллер…ПАМЯТЬ

Память микроконтроллера предназначена для хранения инструкций программы и данных. В микроконтроллерах с Гарвардской архитектурой она разделена на отдельные блоки: память программ (Program Memory) и память данных (Data Memory).

Память программ

Программа микропроцессора представляет собой последовательность команд (инструкций). Каждая инструкция имеет свой оригинальный двоичный код. Коды… Память программ состоит из множества ячеек определенной разрядности, каждая из… Память программ, по существующей классификации, всегда является какой либо разновидностью постоянной памяти (ROM -…Масочная память

Масочная память (maskROM) программируется с помощью фотошаблонов (масок) на стадии изготовления микроконтроллера. Т.е. контроллер с масочной памятью…Однократно программируемая память

Однократно программируемая память (OTPROM - One Time Programmable ROM) no принципу построения и функционирования аналогична масочной, но она… Контроллеры с OTPROM относительно дешевы. Их применение целесообразно при…Репрограммируемая память

Репрограммируемая память (EPROM - Erasable PROM) аналогична OTPROM, но допускает стирание информации и повторное программирование. Стирание… Стоимость контроллеров с EPROM относительно велика и изделия с такой памятью…Память с электрическим стиранием

Память с электрическим стиранием (EEPROM - Electrically EPROM) программируется пользователем и может многократно стираться. Стирание и повторное… Контроллеры с EEPROM относительно дешевы (по сравнению с EPROM), но емкость…Флэш - память

Флэш-память (Flash memory) относится к классу EEPROM, но использует особую технологию построения запоминающих ячеек. В отличие от EEPROM, она может… Современные технологии изготовления Flash Memory обеспечивают гарантированное… Флэш-память программ микроконтроллера может быть переписана самим микроконтроллером. Для организации этого режима в…Память данных

Память данных предназначена для хранения результатов вычислений в процессе работы микроконтроллера. Она организована, как и память программ, в виде множества ячеек, каждая из которых имеет свой адрес. В процессе работы микроконтроллер обращается к ячейкам памяти данных при выполнении команд загрузки (чтения) и записи.

Память данных микроконтроллера может быть двух типов: SRAM и EEPROM.

Статическая память

Статическая память (SRAM - Static Random Access Memory) энергозависима. Она обеспечивает хранение информации только при наличии напряжения питания… Каждая ячейка статической памяти в микроконтроллере имеет свой адрес.… Например, микроконтроллер ATmega 163 имеет 1024 восьмибитные ячейки встроенной статической памяти типа SRAM. Объем…Специализированные ячейки флэш-памяти

В энергонезависимой flash-памяти микроконтроллеров могут присутствовать специализированные биты и байты, предназначенные для защиты программы… 0 Биты блокировки (lock-bits) LB1 и LB2, позволяющие запретить чтение… Запрограммированные биты блокировки можно стереть только при очистке flash -памяти программ. При этом уничтожается и…ПРОЦЕССОРНОЕ ЯДРО

Основные элементы

Каждый производитель микроконтроллеров для серии выпускаемых им изделий разрабатывает и патентует своё оригинальное процессорное ядро (MCU -… 0 регистр инструкций, 0 программный счетчик,Регистр инструкций

Регистр инструкций (IR - Instruction register) - регистр, предназначенный для хранения считанной из памяти программ инструкции. Считанная из памяти… Например, ядро AVR в своей структуре имеет 16-битный регистр инструкций. Эта…Арифметико-логическое устройство

Арифметико-логическое устройство (ALU - Arithmetic Logic Unit) - логическая схема, непосредственно осуществляющая преобразование одной или двух… Типовые арифметические операции ALU: 0 сложение (addition), ° вычитание… 0 инкремент (increment),Регистры общего назначения

Например, ядро AVR имеет 32 регистра общего назначения(GPR - General purpose registers). Каждому регистру (рис. 3.1) соответствует дополнительно…Регистр состояния

Регистр состояния (Status register) предназначен для хранения отдельных признаков результата, полученного при выполнении различных арифметических и… 0 флаг переноса (Carry) - устанавливается при возникновении переноса из старшего разряда результата;Стек

Стек - память данных, организованная по принципу: последний зашел - первый вышел (LIFO - Last In - First Out). Такая память предназначается, обычно, для оперативного сохранения содержимого отдельных регистров при переходах к подпрограммам. Одним из таких регистров является программный счетчик. Извлечение из стека содержимого регистров производится в порядке, обратном порядку записи. Запись в стек и извлечение из стека не требует знания адреса ячеек памяти, в которые записываются данные.

Стек может быть организован либо в специально созданных в ядре ячейках памяти, либо в области SRAM. В последнем случае в ядре предусматривается специальный регистр - указатель стека (Stack Pointer). Указатель стека хранит адрес последней записанной ячейки памяти в области стека. Поскольку при последовательной записи адреса ячеек всегда изменяются последовательно в сторону уменьшения, а при изображении памяти SRAM ячейки с меньшими номерами рисуются сверху, то говорят, что стек при записи растет вверх.

Количество ячеек памяти (количество уровней стека), которые используются в стеке для хранения данных, именуется глубиной стека. Глубина стека в различных архитектурах ядра может быть различна: от 2-х ячеек до размера SRAM. Например, в ядре PIC12 фирмы Microchip заложен 2-х уровневый стек, разрядность ячеек которого равна разрядности памяти программ (12 бит), а в ядре PIC16 той же фирмы - 8 уровневый стек с разрядностью ячеек 13 бит.

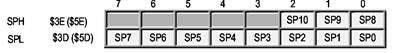

В микроконтроллерах AVR стек организуется в памяти данных типа SRAM. Например, микроконтроллер АТтеgа163 оснащен 16-разрядным указателем стека, размещенным в двух регистрах SPH (Stack Pointer High) и SPL (Stack Pointer Low) пространства ввода/вывода по адресам $3E ($5E) и $3D ($5D). Поскольку рассматриваемый микроконтроллер имеет SRAM с адресами от $000 до $045F (рис. 2.2), то в нем используется только 11 бит указателя стека SP0. ..SP10 (рис. 3.5).

|

Рис. 3.5. Регистры указателя стека микроконтроллера ATmegal63

Указатель стека (SP) указывает на область в статической памяти данных, в которой размещаются стек. Начальное значение указателя стека должно задаваться в программе до первого вызова подпрограмм. Содержимое указателя стека уменьшается на единицу, при каждом занесении данных в стек, и на две единицы при занесении в стек содержимого программного счетчика. Указатель стека увеличивается на единицу, при извлечении данных из стека, и на две единицы при извлечении из стека содержимого программного счетчика. Для работы со стеком в системе команд микроконтроллера предусматриваются специальные инструкции.

Система команд

Мнемонические обозначения

Каждая архитектура микроконтроллера имеет собственную систему команд. Система команд микроконтроллера описывается на специальном языке… adc add with carry сложить с переносом, …Адресация данных

Адреса операндов, задействованных в выполнении любой инструкции программы, в явном или в неявном виде должны быть указаны в коде этой инструкции.… Например, в архитектуре AVR большинство команд занимает только одну ячейку…Косвенная адресация

Косвенным образом могут адресоваться ячейки памяти данных или памяти программ. · Операции с памятью данныхКлассификация команд

Множество инструкций микроконтроллера образует систему команд. Система команд, как правило, не меняется для всех микроконтроллеров одного семейства. В полном списке инструкций при описании системы обычно выделяются отдельные группы, родственных по применению инструкций, например, арифметические и логические команды, команды пересылки и др. Это деление довольно условно и полностью определяется политикой разработчика.

При описании системы команд приводится полная информация о каждой инструкции: способах адресации, использовании флагов регистра состояния, времени исполнения.

В качестве примера рассмотрим систему команд микроконтроллера ATmega 163. Система команд микроконтроллера содержит 130 команд, условно разделенных на четыре группы:

0 команды пересылки данных (data transfer instructions),

0 арифметические и логические команды (arithmetic and logic instructions),

0 команды работы с битами (bit and bit-test instructions),

0 команды ветвления (branch instructions).

При описании системы команд использованы следующие обозначения:

0 Rd - регистр-приемник результата (0 ≤ d ≤ 31),

0 Rd* - регистр-приемник результата с номером более 16 (16 ≤ d ≤ 31),

0 Rr - регистр-источник (0 ≤ r ≤ 31),

0 Rdl: регистры R24, R26, R28, R30 (для инструкций ADIW и SBIW),

0 P- адрес регистра ввода/вывода,

0 P*- адрес побитно адресуемого регистра ввода/вывода ($00-$1F)

0 K - символьная или численная константа (8 бит)

0 k - адресная константа

0 b - номер бита в регистре (3 бита)

0 s - номер бита в регистре статуса (3 бита)

0 X, Y, Z - регистры косвенной адресации (X=R27:R26, Y=R29:R28; Z=R31 :R30

Команды пересылки

Команды пересылки осуществляют перемещение данных между ячейками памяти и регистрами процессорного ядра. Один из операндов, участвующих в инструкции, является источником данных, второй - приемником. При пересылке из источника в приемник копия данных всегда остается в источнике. Таким образом, все команды пересылки практически осуществляют копирование данных.

Одним из операндов в любой команде пересылки обычно является регистр общего назначения процессорного ядра. Вторым может быть любой регистр или ячейка памяти.

Инструкции, как правило, не влияют на флаги в регистре состояния процессорного ядра.

В системе команд микроконтроллеров AVR предусмотрено 34 инструкции, осуществляющие пересылку данных. В инструкциях используются все, за исключением битовых, способы адресации данных; одним из операндов в любой инструкции является регистр общего назначения. Инструкция ldi (load immediate), использующая непосредственную адресацию, может быть использована только в старшей половине файла регистров общего назначения (R16....R31), остальные команды работают с любым из регистров файла. Инструкцию spm (store program memory), осуществляющую запись кода в память программ, можно использовать только в Boot Program Section памяти программ.

Время выполнения инструкций, работающих с регистрами, равно 1 такту. Инструкции, обращающиеся к ячейкам памяти данных, выполняются за 2 такта, а обращающиеся к ячейкам памяти программ - за 3 такта.

Таблица. 3.1. Команды пересылки AVR-микроконтроллеров

| Мнемоника | Операнды | Описание инструкции | Выполняемая операция | Флаги | Такты | ||

| mov | Rd, Rr | Move Between Registers | Rd<- Rr | None | |||

| movw | Rd, Rr | Copy Register Word | Rd+1:Rd<- Rr+1:Rr | None | |||

| ldi | Rd*, K | Load Immediate | Rd<- K | None | |||

| ld | Rd, X | Load Indirect | Rd<- (X) | None | |||

| ld | Rd, X+ | Load Indirect and Post-Inc. | Rd <- (X), X <- X + 1 | None | |||

| ld | Rd,-X | Load Indirect and Pre-Dec. | X<-X-1,Rd<- (X) | None | |||

| ld | Rd, Y | Load Indirect | Rd <- (Y) | None | |||

| ld | Rd, Y+ | Load Indirect and Post-Inc. | Rd <- (Y), Y <- Y + 1 | None | |||

| ld | Rd,-Y | Load Indirect and Pre-Dec. | Y<-Y-1,Rd<- (Y) | None | |||

| ldd | Rd, Y+q | Load Indirect with Displacement | Rd<- (Y + q) | None | |||

| ld | Rd, Z | Load Indirect | Rd<- (Z) | None | |||

| ld | Rd, Z+ | Load Indirect and Post-Inc. | Rd <- (Z), Z <- Z+1 | None | |||

| ld | Rd,-Z | Load Indirect and Pre-Dec | Z<- Z-1,Rd<- (Z) | None | |||

| ldd | Rd, Z+q | Load Indirect with Displacement | Rd<- (Z + q) | None | |||

| lds | Rd, k | Load Direct from SRAM | Rd<- (k) | None | |||

| ST | X, Rr | Store Indirect | (X)<- Rr | None | |||

| st | X+, Rr | Store Indirect and Post-Inc. | (X) <- Rr, X <- X + 1 | None | |||

| st | -X, Rr | Store Indirect and Pre-Dec. | X<- X-1,(X)<- Rr | None | |||

| st | Y, Rr | Store Indirect | (Y) <- Rr | None | |||

| st | Y+, Rr | Store Indirect and Post-Inc. | (Y) <- Rr, Y <- Y + 1 | None | |||

| st | -Y, Rr | Store Indirect and Pre-Dec. | Y<- Y-1,(Y)<- Rr | None | |||

| std | Y+q,Rr | Store Indirect with Displacement | (Y + q)<- Rr | None | |||

| st | Z, Rr | Store Indirect | (Z) <- Rr | None | |||

| st | Z+, Rr | Store Indirect and Post-Inc. | (Z) <- Rr, Z <- Z + 1 | None | |||

| st | -Z, Rr | Store Indirect and Pre-Dec | Z<- Z-1,(Z)<- Rr | None | |||

| std | Z+q,Rr | Store Indirect with Displacement | (Z + q)<- Rr | None | |||

| sts | k, Rr | Store Direct to SRAM | (k)<- Rr | None | |||

| lpm | Load Program Memory | R0<- (Z) | None | ||||

| lpm | Rd, Z | Load Program Memory | Rd<-Z) | None | |||

| lpm | Rd, Z+ | Load Program Memory and Post-Inc. | Rd <- (Z), Z=Z+1 | None | |||

| spm | Store Program Memory | (Z)<- R1:R0 | None | - | |||

| in | Rd, P | In Port | Rd<- P | None | |||

| out | P, Rr | Out Port | P<- Rr | None | |||

| push | Rr | Push Register on Stack | STACK <- Rr; SP<- SP-1 | None | |||

| pop | Rd | Pop Register from Stack | SP<- SP+1, Rd<- STACK | None | |||

Арифметические и логические команды

В группу арифметических команд входят команды выполняющие сложение, вычитание, декремент и инкремент данных, логическое умножение, логическое сложение, операцию ИСКЛЮЧАЮЩЕЕ ИЛИ, инверсию переменной. Обычно к этой группе относят также инструкции сравнения данных. В микроконтроллере АТтеда163 реализованы также функции арифметического умножения целых чисел и дробных чисел, без знака и со знаком.

Все инструкции этой группы, как правило, приводят к изменению состояния флагов регистра состояния в соответствии с результатами, выполняемой операции.

В микроконтроллерах с архитектурой AVR предусмотрено довольно много (31) инструкций, выполняющих арифметические и логические преобразования данных. Инструкции используют исключительно прямую регистровую или непосредственную адресацию данных. Операнды хранятся в регистрах общего назначения, в один из них (регистр-приемник) всегда направляется и результат вычислений.

В результате выполнения инструкций изменяются флаги регистра SREG (Status Register), а флаг переноса С (Carry), кроме того, непосредственно участвует в выполнении ряда операций.

Арифметические команды сложения и вычитания выполняют сложение и вычитание одно- и двухбайтных операндов. Команды adc (add with carry two registers) и sbc (subtract with carry two registers) используют при вычислениях флаг переноса С.

Инструкции логического умножения (and) и логического сложения (or), ИСКЛЮЧАЮЩЕЕ ИЛИ (eor) преобразуют только однобайтные данные.

Инструкция дополнения до единицы com (one's complement), фактически выполняет операцию инверсии, а инструкция дополнения до двух neg (two's complement) - меняет знак числа.

Инструкции установки (set) позволяют установить как отдельные, так и все биты выбранного регистра в единичное состояние, а команды очистки (clear) - в нулевое.

Инструкции инкремента регистра inc (increment) и декремента регистра dec (decrement) используют прямую адресацию одного выбранного регистра.

Тест на нуль или минус tst (test for гею or minus) фактически не меняет содержимого регистра, но устанавливает соответствующие флаги при равенстве операнда нулю или при его отрицательном значении.

Команды сравнения (compare) также не меняют содержимого регистров, а оценивают разность операндов и устанавливают соответствующие флаги в регистре состояния.

Шесть инструкций умножения (multiply) выполняют умножение целых и дробных операндов с учетом и без учета знака. 16-битный результат умножения всегда записывается в регистры общего назначения R0:R1.

Большинство арифметических и логических команд выполняются за один такт. Исключение составляют только команды с непосредственной адресацией, работающие с двухбайтными словами: adiw (add immediate to word) и sbiw (subtract immediate from word), и команды умножения, выполняющиеся за два такта.

Таблица 3.2. Арифметические и логические команды микроконтроллера Atmega163

| Мнемо- ника | Операнды | Описание | Операция | Флаги | Такm | |

| add | Rd, Rr | Add without Carry two Registers | Rd <- Rd + Rr | Z,C,N,V,H | ||

| adc | Rd, Rr | Add with Carry two Registers | Rd <- Rd + Rr + C | Z,C,N,V,H | ||

| adiw | Rdl, K | ADD Immediate from Word | Rdh:Rdl <- Rdh:Rdl+K | Z,C,N,V,S | ||

| sub | Rd, Rr | Subtract without Carry two Registers | Rd<- Rd-Rr | Z,C,N,V,H | ||

| subi | Rd*, K | Subtract Constant from Register | Rd<- Rd-K | Z,C,N,V,H | ||

| sbc | Rd, Rr | Subtract with Carry two Registers | Rd<- Rd-Rr-C | Z,C,N,V,H | ||

| sbci | Rd*, K | Subtract with Carry Constant from Register | Rd<- Rd-K-C | Z,C,N,V,H | ||

| sbiw | Rdl, K | Subtract Immediate from Word | Rdh:Rd <- Rdh:Rdl- K | Z,C,N,V,S | ||

| and | Rd, Rr | Logical AND Registers | Rd <- Rd Rr | Z,N,V | ||

| andi | Rd*, K | Logical AND Register and Constant | Rd <- Rd K | Z,N,V | ||

| or | Rd, Rr | Logical OR Registers | Rd <- Rd v Rr | Z,N,V | ||

| ori | Rd*, K | Logical OR Register and Constant | Rd<- RdvK | Z,N,V | ||

| eor | Rd, Rr | Exclusive OR Registers | Rd <- Rd Rr | Z,N,V | ||

| com | Rd | One's Complement | Rd <- $FF - Rd | Z,C,N,V | ||

| neg | Rd | Two's Complement | Rd<- $00-Rd | Z,C,N,V,H | ||

| sbr | Rd*, K | Set Bit(s) in Register | Rd<- RdvK | Z,N,V | ||

| ser | Rd | Set Register | Rd <- $FF | None | ||

| cbr | Rd*, K | Clear Bit(s) in Register | Rd <- Rd ($FF - K) | Z,N,V | ||

| clr | Rd | Clear Register | Rd <- $00 | Z,N,V | ||

| inc | Rd | Increment | Rd <- Rd + 1 | Z,N,V | ||

| dec | Rd | Decrement | Rd<- Rd-1 | Z,N,V | ||

| tst | Rd | Test for Zero or Minus | Rd <- Rd Rd | Z,N,V | ||

| ср | Rd, Rr | Compare | Rd-Rr | Z, N,V,C,H | ||

| срс | Rd, Rr | Compare with Carry | Rd-Rr-C | Z, N,V,C,H | ||

| cpi | Rd*, K | Compare Register with Immediate | Rd-K | Z, N,V,C,H | ||

| mul | Rd, Rr | Multiply Unsigned | R1:R0<-RdxRr | Z,C | ||

| muls | Rd, Rr | Multiply Signed | R1:R0<-RdxRr | Z,C | ||

| mulsu | Rd, Rr | Multiply Signed with Unsigned | R1:R0<-RdxRr | Z,C | ||

| fmul | Rd, Rr | Fractional Multiply Unsigned | R1:R0<-(RdxRr)«1 | Z,C | ||

| fmuls | Rd, Rr | Fractional Multiply Signed | R1:R0<-(RdxRr)«1 | Z,C | ||

| fmulsu | Rd, Rr | Fractional Multiply Signed with Unsigned | R1:RCX-(RdxRr)«1 | Z,C | ||

Битовые команды

Битовые команды (Bit And Bit-Test Instructions) позволяют обращаться непосредственно к отдельным битам регистров процессорного ядра и выполнять с выбранными битами простейшие операции: пересылки, установки и сброса. Операндами команд могут быть как биты регистров общего назначения, так и биты регистров ввода/вывода. Битовые команды могут влиять на отдельные флаги регистра признаков.

Битовые команды микроконтроллеров семейства AVR работают с отдельными битами регистров общего назначения и регистров ввода/вывода. Биты регистров ввода/вывода могут быть установлены или сброшены. Биты регистров общего назначения могут быть сдвинуты в соседние ячейки, как влево (в сторону старших разрядов), так и вправо (в сторону младших разрядов). В операциях сдвига, кроме разрядов регистров, может участвовать и бит переноса. Специальные команды предусмотрены для установки и сброса отдельных флагов регистра состояния. Команда swap меняет местами тетрады (полубайты) регистров общего назначения.

Таблица 3.3. Битовые команды микроконтроллера АТтеда163

| Мнемо- ника | Операнды | Описание | Операция | Флаги | Так m |

| sbi | P*,b | Set Bit in I/O Register | I/O(P,b) <-1 | None | |

| cbi | P*,b | Clear Bit in I/O Register | I/O(P,b) <- 0 | None | |

| lsl | Rd | Logical Shift Left | Rd(n+1) <- Rd(n), Rd(0) <- 0 | Z,C,N,V | |

| lsr | Rd | Logical Shift Right | Rd(n)<-Rd(n+1), Rd(7)<-0 | Z,C,N,V | |

| rol | Rd | Rotate Left Through Carry | Rd(0)<-C, Rd(n+1)<- Rd(n), C <- Rd(7) | Z,C,N,V | |

| гог | Rd | Rotate Right Through Carry | Rd(7) <- C,Rd(n)<- Rd(n+1),C<-Rd(0) | Z,C,N,V | |

| asr | Rd | Arithmetic Shift Right | Rd(n)<-Rd(n+1), n=0..6 | Z,C,N,V | |

| swap | Rd | Swap Nibbles | Rd(3..0)<-Rd(7..4), Rd(7..4) <-Rd(3..0) | None | |

| bset | s | Flag Set | SREG(s) <-1 SREG(s) | ||

| bclr | s | Flag Clear | SREG(s) <- 0 SREG(s) | ||

| bld | Rd, b | Bit load from T to Register | Rd(b) <- T | None | |

| bst | Rr, b | Bit Store from Register to T | T <- Rr(b) | T | |

| sec | Set Carry | C<-1 | С | ||

| clc | Clear Carry | C<-0 | с | ||

| sen | Set Negative Flag | N<-1 | N | ||

| cln | Clear Negative Flag | N<-0 | N | ||

| sez | zSet Zero Flag Z <-1 | z | |||

| clz | Clear Zero Flag | Z<-0 | z | ||

| sei | Global Interrupt Enable | K-1 | I | ||

| cli | Global Interrupt Disable | <-0 | I | ||

| ses | Set Signed Test Flag | S<-1 | s | ||

| cls | Clear Signed Test Flag | S<-0 | s | ||

| sev | Set Twos Complement Overflow | V<-1 | V | ||

| clv | Clear Twos Complement Overflow | V<-0 | V | ||

| set | SetTinSREG | T<-1 | T | ||

| clt | Clear T in SREG | T<-0 | T | ||

| she | Set Half Carry Flag in SREG | H<-1 | H | ||

| clh | Clear Half Carry Flag in SREG | H<-0 | H |

Инструкции ветвления

Инструкции ветвления изменяют содержимое программного счетчика. Они используются при организации переходов и подпрограмм. Инструкции условных переходов и условных вызовов подпрограмм в процессе исполнения проверяют выполнение различных условий. Если условие не выполняется, программный счетчик просто инкрементируется. Такими условиями может быть равенство содержимого двух регистров, единичное или нулевое состояние заданных битов в регистрах общего назначения, регистрах ввода/вывода или в регистре состояния, Например, команда cpse (compare, skip if equal) проверяет равенство содержимого регистров, команда sbrc Rr, b (skip if bit in register cleared) осуществляет переход при условии равенства нулю содержимого бита b в регистре Rr, а инструкция brmi k (branch if minus) проверяет флаг отрицательного результата (N) в ретстре состояния SREG.

Время выполнения команд ветвления зависит от результата проверки. Оно, для различных инструкций, может меняться, в пределах от одного до четырех тактов.

Таблица 3.4. Команды переходов микроконтроллера АТтеда163

| Мнемоника | Операн ды | Описание | Операция | Флаги | Такт |

| rjmp | k | Relative Jump | PC <- PC + k + 1 | None | |

| ijmp | Indirect Jump to (Z) | PC<-Z | None | ||

| jmp | k | Jump | PC<-k | None | |

| rcall | k | Relative Subroutine Call | PC <- PC + k + 1 | None | |

| call | k | Call Subroutine | PC<-k | None | |

| icall | Indirect Call to (Z) | PC<-Z | None | ||

| ret | Subroutine Return | PC <- STACK | None | ||

| reti | Interrupt Return | PC <- STACK | I | ||

| cpse | Rd,Rr | Compare, Skip if Equal | if (Rd = Rr) PC <- PC + 2 or3 | None | 1/2/ 3 |

| sbrc | Rr, b | Skip if Bit in Register Cleared | if(Rr(b)=0) PC<-PC + 2 or3 | None | 1/2 |

| sbrs | Rr, b | Skip if Bit in Register is Set | if (Rr(b)=1)PC<-PC + 2 or3 | None | 1/2 |

| sbic | P*, b | Skip if Bit in I/O Register Cleared | if (P(b)=0) PC <- PC + 2 or 3 | None | 1/2 |

| sbis | P*, b | Skip if Bit in I/O Register is Set | if(P(b)=1)PC<-PC + 2or 3 | None | 1/2 |

| brbs | s, k | Branch if Status Flag Set | if(SREG(s)=1)thenPC <- PC+k + 1 | None | 1/2 |

| brbc | s, k | Branch if Status Flag Cleared | if(SREG(s) = 0) then PC <- PC+k + 1 | None | 1/2 |

| breq | k | Branch if Equal | if(Z=1)thenPC<-PC + k+1 | None | 1/2 |

| brcs | k | Branch if Carry Set | if(C=1)thenPC<-PC + k+ 1 | None | 1/2 |

| brne | k | Branch if Not Equal | if (Z = 0) then PC <- PC + k+1 | None | 1/2 |

| brcc | k | Branch if Carry Cleared | if (C = 0) then PC <- PC + k+ 1 | None | 1/2 |

| brsh | k | Branch if Same or Higher | if (C = 0) then PC <- PC + k+ 1 | None | 1/2 |

| brlo | k | Branch if Lower | if(C=1)thenPC<-PC + k+1 | None | 1/2 |

| brmi | k | Branch if Minus | if (N = 1)thenPC<-PC + k+ 1 | None | 1/2 |

| brpl | k | Branch if Plus | if (N = 0) then PC <- PC + k+1 | None | 1/2 |

| brge | k | Branch if Greater or Equal, Signed | if (N © V= 0) then PC <- PC + k + 1 | None | 1/2 |

| brlt | k | Branch if Less Than Zero, Signed | if (N®V= 1)thenPC<- PC + k + 1 | None | 1/2 |

| brhs | k | Branch if Half Carry Flag Set | if(H = 1)thenPC<-PC + k+1 | None | 1/2 |

| brhc | k | Branch if Half Carry Flag Cleared | if (H = 0) then PC <- PC + k+ 1 | None | |

| brts | k | Branch if T Flag Set | if (T = 1)thenPC<-PC + k+1 | None | 1/2 |

| brtc | k | Branch if T Flag Cleared | if (T = 0) then PC <- PC + k+ 1 | None | 1/2 |

| brvs | k | Branch if Overflow Flag is Set | if (V = 1)thenPC<-PC + k+1 | None | 1/2 |

| brvc | k | Branch if Overflow Flag is Cleared | if (V = 0) then PC <- PC + k+1 | None | 1/2 |

| brie | k | Branch if Interrupt Enabled | if (I = 1)thenPC<-PC + k+ 1 | None | 1/2 |

| brid | k | Branch if Interrupt Disabled | if (I = 0) then PC <- PC + k+1 | None | 1/2 |

Инструкции управления

Инструкции управления используются для управления вычислениями и режимами работы процессорного ядра. Пустая операция nop заполняет пробелы между инструкциями в программной памяти или используется в качестве выдержки. Команда sleep переводит процессорное ядро в режим пониженного энергопотребления. Инструкция wdr сбрасывает сторожевой таймер.

Таблица 3.5. Инструкции управления микроконтроллера АТтеда163.

| Мнемоника | Описание | Операция | Такт |

| пор | No Operation | None | |

| sleep | Sleep (see specific description) | None | |

| wdr | Watchdog Reset | None |

ЯЗЫК АССЕМБЛЕРА

Язык ассемблера (assembler language) - язык программирования микропроцессорных систем, ориентированный на определенную архитектуру системы.… Язык ассемблера использует систему команд процессорного ядра и специальные… Компилятор транслирует исходные коды с языка ассемблера в объектный код. Полученный объектный может быть…Выражения

Программа на языке ассемблера состоит из отдельных строк. Строка кода не должна быть длиннее 120 символов. Ассемблер Atmel AVR не различает строчные… Любая строка может начинаться с метки, которая является набором символов,…Операнды

Операндами языка ассемблера могут быть: 0 Определяемые пользователем метки.Операторы

Все операторы ассемблера перечислены в таблице. Порядок выполнения операторов в выражении определяется приоритетом. Операторы с большим приоритетом выполняются в первую очередь. Кроме того, отдельные выражения могут быть заключены в круглые скобки. Такие выражения также вычисляются в первую очередь.

Таблица 4.1. Операторы языка Atmel AVR Assembler

| Символ | Описание | Приоритет | |

| ! | Logical Not | Логическое НЕ | |

| - | Bitwise Not | Побитное НЕ | |

| - | Unary Minus | Смена знака | |

| * | Multiplication | Умножение | |

| 1 | Division | Деление | |

| + | Addition | Сложение | |

| - | Subtraction | Вычитание | |

| « | Shift left | Сдвиг влево | |

| » | Shift right | Сдвиг вправо | |

| < | Less than | Меньше | |

| <= | Less than or equal | Меньше или равно | |

| > | Greater than | Больше | |

| >= | Greater than or equal | Больше или равно | |

| == | Equal | Равно | |

| != | Not equal | Не равно | |

| & | Bitwise And | Побитное И | |

| Л | Bitwise Xor | Побитное ИСКЛЮЧАЮЩЕЕ ИЛИ | |

| | | Bitwise Or | Побитное ИЛИ | |

| && | Logical And | Логическое И | |

| Logical Or | Логическое ИЛИ |

Логическое НЕ

Оператор | возвращает 1, если выражение равно 0, в противном случае возвращает 0

Например: ldir16,!$fO ; в регистр r16 пересылается $00

Побитное НЕ

Оператор ~ возвращает побитную инверсию выражения. Например: ldi M6,~$fO; в регистр r16 пересылается $0f

Смена знака

Оператор - возвращает отрицание арифметического выражения Например: ldi r16,-2 ; пересылается число-2 ($fe) в регистр r16

Умножение

Оператор * возвращает произведение выражений

Например: ldi r30,label*2; пересылается в регистр r30 произведение label*2

Деление

Оператор / возвращает целую часть от деления левой части выражения на правую. Наример: ldi r30,label/2; пересылается в регистр r30 целая часть выражения label/2.

Сложение

Оператор + возвращает сумму двух выражений

Пример: ldi гЗО,с1+с2 ; пересылается в регистр r30 сумма с1+с2

Вычитание

Оператор - возвращает разность двух выражений. Например: ldi r17,с1-с2 ;пересылается в r17 разность с1-с2

Сдвиг влево

Оператор « возвращает левое выражение сдвинутое влево на количество бит, указанных в правом выражении.

Например: ldi r17,1«bitmask; Пересылается в регистр r17 число 1 сдвинутое влево на bitmask бит.

Сдвиг вправо

Оператор » возвращает выражение в левой части сдвинутое вправо на количество бит, указанных в правой части.

Например: ldi r17,с1»с2 ;пересылается в регистр r17 число с1 сдвинутое вправо на c2 бит.

Меньше

Оператор < возвращает 1, если выражение в левой части меньше, чем выражение в правой; О-в противном случае

Например: ori r18,bitmask*(c1<c2)+1 выполняется логическое ИЛИ регистра r18 с результатом вычислений bitmask*(c1<c2)+1

Меньше или равно

Оператор <= возвращает 1, если выражение в левой части меньше или равно, чем выражение в правой части; О-в противном случае

Например: ori M8,bitmask*(c1<=c2)+1 ; логическое ИЛИ r18 с результатом вычисления выражения.

Больше

Оператор > возвращает 1, если выражение со знаком слева больше, чем выражение со знаком справа; О-в противном случае.

Например: ori r18,bitmask*(c1>c2)+1 ; логическое ИЛИ r18 с выражением .

Больше или равно

Оператор >= возвращает 1, если выражение в левой части больше или равно, выражению в правой; О-в противном случае..

Например: ori r18,bitmask*(c1>=c2)+1 ; логическое ИЛИ r18 с выражением.

Равно

Оператор == возвращает 1, если выражение в левой части равно, выражению в правой; О-в противном случае..

Например: andi r19 ,bitmask*(c1 ==с2)+1 ; логическое И r19 с выражением

Не равно

Оператор |= возвращает 1, если выражение в левой части не равно, выражению в правой; О-в противном случае..

Например: .set flag=(c1 |=c2) ; установка переменной flag Побитное И

Оператор & возвращается поразрядное логическое И между двумя выражениями Например: ldi r18,High(c1&c2) ; пересылка в r18 выражения

Побитное ИСКЛЮЧАЮЩЕЕ ИЛИ

Оператор ^ возвращается поразрядное ИСКЛЮЧАЮЩЕЕ ИЛИ между двумя выражениями

Например: ldi r18,Low(dAc2) ;пересылка в r18 выражения

Побитное ИЛИ

Оператор | возвращается поразрядное ИЛИ между двумя выражениями Пример: ldi r8,Low(c1 |c2); пересылка в r 8 выражения

Логическое И

Оператор && возвращается 1, если оба выражения отличны от нуля; О-в остальных случаях

Например: ldi r18,Low(c1&&c2) ; пересылка в r1 8 выражения

Логическое ИЛИ

Оператор || возвращает 1, если один или оба из выражения отличны от нуля, О-в остальных случаях.

Например: ldi r18,Low(d||c2) ; пересылка в r8 выражения

Функции

Функции, определенные в языке ассемблера 0 low(expression) возвращает младший байт выражения; 0 high(expression) возвращает второй байт выражения;Директивы

Директивы ассемблера не транслируются в коды операций, они используются для размещения программы в памяти, определяют макрокоманды, инициализируют… Таблица 4.2. Директивы языка Atmel AVR AssemblerТАКТОВЫЙ ГЕНЕРАТОР

Работа процессорного ядра синхронизируется тактовым генератором. Именно период работы генератора определяет время, необходимое для выполнения… Схемы тактовых генераторов могут быть различны. Простейшим и наиболее дешевым считается внутренний (реализованный на кристалле) RC-генератор. Он строится без внешних…СИСТЕМА СБРОСА

Сбросом считается перевод микроконтроллера в исходное состояние. При этом все регистры микропроцессорного ядра устанавливаются во вполне определенные начальные состояния, и микроконтроллер переходит к выполнению программы с фиксированного начального адреса. Таким адресом обычно является адрес $0.

Источники сброса

Причинами (источниками) сброса могут являться различные воздействия: включение питания и кратковременные его изменения, сигналы формируемые…Сторожевой таймер

Сторожевой таймер (Watchdog) синхронизирован от отдельного внутреннего генератора на кристалле, работающего с частотой 1 МГц (при напряжении питания… Задержка сброса устанавливается с помощью предделителя (Prescaler). Настройка…СИСТЕМА ПРЕРЫВАНИЙ

Алгоритм обработки прерываний

Сигнал запроса на прерывание вырабатывается периферийным устройством при его готовности к обмену информацией. Сигнал может появиться в произвольный… Процессорное ядро может реагировать на запросы прерываний по-разному. В каждой… 0 при поступлении запроса на прерывание завершается выполнение текущей инструкции программы;Вектора прерываний

Идентификация источника прерывания в системе может выполняться как программными, так и аппаратными средствами. В первом случае, источник прерывания фиксируется установкой флажка в каком… Во втором случае каждому источнику прерываний ставится в соответствие определенный адрес программы (вектор прерывания)…ЭНЕРГОНЕЗАВИСИМАЯ ПАМЯТЬ ДАННЫХ

Энергонезависимая память типа EEPROM отличается от памяти данных типа SRAM существенно большим временем чтения и записи информации. Время обращения… 0 регистр статуса микроконтроллера SREG,ПОРТЫ ВВОДА-ВЫВОДА

9.1. Организация ввода/вывода Порты ввода-вывода обеспечивают ввод и вывод данных в параллельном формате. Обычно порты ввода-вывода выполняются…Алгоритмы обмена данными

Порты ввода-вывода предназначены для связи микроконтроллера с различными объектами и могут реализовывать различные алгоритмы обмена данными: 0… Обмен данными между портами и объектами обеспечивается специальными…АНАЛОГО-ЦИФРОВЫЕ ПРЕОБРАЗОВАТЕЛИ

Аналого-цифровой преобразователь ADC (Analog Digital Converter) осуществляет преобразование напряжения в цифровой код. Он предназначен для оцифровки и ввода в микроконтроллер аналоговых сигналов с различных датчиков физических величин. Схемы преобразователей различны. В зависимости от принципа построения меняются и свойства преобразователя.

Принципы аналого-цифрового преобразования

В параллельном преобразователе (рис. 10.1) входной сигнал подается сразу на…Управление аналого-цифровым преобразователем

В состав микроконтроллеров обычно включают 8 - 16-битные многоканальные преобразователи с большим набором встроенных функций. При этом все функции… Например, микроконтроллер ATmega163 оснащен 10-разрядным ADC последовательных…АНАЛОГОВЫЕ КОМПАРАТОРЫ

Рис.11.1. Структурная схема аналогового компаратораТАЙМЕРЫ-СЧЕТЧИКИ

Большинство задач управления решаются в реальном времени. При этом микроконтроллер должен в определенные моменты времени выполнять определенные… 0 подсчет импульсов сигнала за фиксированный интервал времени; 0 формирование интервалов времени определенной длительности;Простейший 8-битный счетчик

8-разрядный таймер/счетчик 0 (Timer/Counter0) тактируется сигналом синхронизации процессорного ядра (СК) или от встроенного предделителя…Захват, сравнение и широтно-импульсная модуляция

16-битный таймер/счетчик Timer/Counter1 микроконтроллера ATmega163 доступен процессорному ядру для чтения и записи, он может считать импульсы… Шесть 16-битных регистров счетчика/таймера обеспечивают хранение данных в…Часы реального времени

Часы реального времени RTC (Real Time Clock) являются разновидностью таймера/счетчика. Задачей RTC в схеме микроконтроллера обычно считается… 8-разрядный таймер/счетчик 2 (Timer/Counter 2) микроконтроллера АТтеда163… При внешнем тактировании таймер/счетчик работает в асинхронном режиме, независимо от тактовых импульсов СК.ПОСЛЕДОВАТЕЛЬНЫЙ ВВОД-ВЫВОД

Интерфейс UART

Асинхронный последовательный интерфейс UART (Universal Asynchronous Receiver Transmitter - универсальный асинхронный приемопередатчик) обеспечивает… В режиме асинхронной передачи каждое слово данных передается автономно и…Интерфейс SPI

Последовательный периферийный интерфейс SPI (Serial Peripheral Interface) предложен фирмой Motorola. Он обеспечивает полный дуплексный обмен данными…РЕЖИМЫ ЭНЕРГОСБЕРЕЖЕНИЯ

Одним из основных показателей микроконтроллера является энергопотребление. Величина энергопотребления характеризуется напряжением питания… По напряжению питания все выпускаемые микроконтроллеры можно условно разделить… 0 Микроконтроллеры с напряжением питания 5,0В±10%. Предназначены для работы в изделиях, питающихся от промышленной или…Режим Idle

Если биты SM1/SM0 находятся в состоянии 00, то команда SLEEP переводит микроконтроллер в режим ожидания Idle. В этом режиме его ток потребления…Режим ADC Noise Reduction

Когда SM1/SM0 биты установлены в 01, команда SLEEP заставит микроконтроллер ввести режим шумоподавления ADC Noise Reduction. В этом режиме… Режим ADC Noise Reduction улучшает шумовую среду для аналого-цифрового… Активизация процессорного ядра происходит при прерываниях от аналого- цифрового преобразователя, от двухпроводного…Режим Power Down

При установке битов SM1/SM0 в состояние 10 команда SLEEP переводит микроконтроллер в режим останова Power Down. В этом режиме его ток потребления менее 1 мкА. При этом останавливается внешний генератор. Пользователь может разрешить работу сторожевого таймера. Если сторожевой таймер разрешен, то активизация процессорного ядра произойдет по завершении установленного в сторожевом таймере периода времени.

Режим Power Save

При установке битов SM1/SM0 в состояние 11 команда SLEEP переводит микроконтроллер в режим экономии Power Save. Этот режим аналогичен режиму Power Down, но если таймер/счетчик 0 тактируется асинхронно, т.е. бит AS0 в регистре ASSR установлен, то в этом режиме таймер/счетчик 0 будет работать и микроконтроллер будет активироваться прерываниями по переполнению или совпадению с выхода таймера/счетчика 0.

ТЕХНОЛОГИИ ПРОГРАММИРОВАНИЯ МИКРОКОНТРОЛЛЕРОВ

Способы программирования энергонезависимой памяти

В процессе программирования микроконтроллеров разработанная пользователем программа заносится в энергонезависимую память. При этом выполняются… 0 операция "Chip erase" (стирание кристалла); 0 чтение/запись FLASH-памяти программ;Программно-аппаратные средства поддержки программирования

Подготовка программ для микроконтроллера выполняется на персональном компьютере и состоит из следующих этапов: 0 создание текста программы; 0 трансляция текста в машинные коды и исправление синтаксических ошибок;ЛИТЕРАТУРА

1. Бродин В.Б., Шагурин М.И. Микроконтроллеры. Архитектура, программирование, интерфейс- М.: Издательство ЭКОМ, 1999.- 400 с.

2. Шагурин И.И. Микропроцессоры и микроконтроллеры фирмы Motorola: Справ, пособие.- М.: Радио и связь, 1998.- 560 с.

3. Однокристальные микроконтроллеры Р1С12С5х, Р1С12С6х, Р1С16х8х, PIC14000, М16С/61/62. Под ред. Б.Я.Прокопенко.- М.: ДОДЕКА, 2000.- 336 с.

4. Микроконтроллеры семейства Z86 фирмы ZILIG. Руководство программиста. М.: 1999,-96 с.

5. Ремизевич Т.В. Микроконтроллеры для встраиваемых приложений: от общих подходов - к семействам HC05 и HC08 фирмы Motorola./ под ред Кирюхина И.С.- М.: ДОДЕКА, 2000.- 272 с.

6. Современные микроконтроллеры: Архитектура, средства проектирования, примеры применения, ресурсы сети Интернет. Под ред. Коршуна И.В.- М.: Издательство «Аким», 1998 - 272 с.

ПРИЛОЖЕНИЯ

Приложение 1. Корпуса микроконтроллера ATmega163 Корпус DIP (Dual In Line pin Package)ГЛОССАРИЙ ТЕРМИНОВ И СОКРАЩЕНИЙ

– Конец работы –

Используемые теги: архитектура, микроконтроллера0.05

Если Вам нужно дополнительный материал на эту тему, или Вы не нашли то, что искали, рекомендуем воспользоваться поиском по нашей базе работ: АРХИТЕКТУРА МИКРОКОНТРОЛЛЕРА

Что будем делать с полученным материалом:

Если этот материал оказался полезным для Вас, Вы можете сохранить его на свою страничку в социальных сетях:

| Твитнуть |

Хотите получать на электронную почту самые свежие новости?

Новости и инфо для студентов