ЭНЕРГОНЕЗАВИСИМАЯ ПАМЯТЬ ДАННЫХ

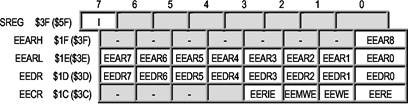

Энергонезависимая память типа EEPROM отличается от памяти данных типа SRAM существенно большим временем чтения и записи информации. Время обращения при записи обычно составляет несколько миллисекунд и к тому же сильно зависит от напряжения питания микроконтроллера. По этой причине обращение к EEPROM всегда осуществляется через регистры ввода/вывода. В ряде случаев в архитектуре микроконтроллера предусматриваются специальные сервисные функции, которая позволяют пользователю программными средствами обнаруживать момент готовности EEPROM к записи. Для индикации момента готовности EEPROM к записи новых данных устанавливаются специальные прерывания по завершению записи EEPROM (EEPROM Write Complete). Случайная запись в EEPROM предотвращается выполнением специальных процедур. Для работы с EEPROM в структуре микроконтроллера всегда предусматривается несколько регистров, хранящих адрес ячейки памяти, данные, команды и флаги состояния памяти. Например, микроконтроллеру ATmega163 для записи байта данных в EEPROM необходимо 1.9 - 3.8 мс. В процессе работы с памятью он использует (рис. 8.1):

0 регистр статуса микроконтроллера SREG,

0 два адресных регистра EEARH и EEARL (EEPROM Address Registers),

0 регистр данных EEDR (EEPROM Data Register),

0 регистр управления EECR (EEPROM Control Register).

|

Рис. 8.1. Регистры, задействованные в управлении EEPROM

Регистры адреса EEPROM (EEPROM Address Registers) EEARH и EEARL позволяют адресовать 512 байт памяти пространства EEPROM.

0 Бит 0 регистра EEARH и биты 7….0 регистра - EEARL - EEAR8…EEAR0

(EEPROM address) образуют 9 битный адрес ячейки памяти. Начальные значения EEAR8….EEAR0 не определены. Обращаться за данными к EEPROM можно только после записи адреса.

Регистр данных EEDR (EEPROM Data Register) хранит данные для записи в EEPROM при выполнении операции записи или данные, считанные из EEPROM, при выполнении операции чтения.

0 Биты 7 .. EEDR7…. EEDR0 (EEPROM Data) - данные EEPROM.

Регистр управления EECR (EEPROM Control Register) предназначен для управления записью и чтением EEPROM.

0 Бит 3 - EERIE (EEPROM Ready Interrupt Enable) - разрешение прерывания по готовности EEPROM. При установленных в состояние 1 бите EERIE и 1-бите регистра SREG разрешается прерывание по готовности EEPROM. При очищенном бите EERIE прерывание запрещено. Запрос прерывания по готовности EEPROM при очищенном бите EEWE генерируется непрерывно. Вектор прерывания EE_RDY имеет адрес $1E.

0 Бит - EEMWE (EEPROM Master Write Enable) - управление разрешением записи EEPROM. Бит EEMWE определяет, будет ли установленный в состояние 1 бит EEWE разрешать запись в EEPROM. При установленном в состояние 1 бите EEMWE установка бита EEWE приведет к записи в EEPROM по заданному адресу. Если же бит EEMWE будет находиться в состоянии 0, то установка бита EEWE никакого эффекта не окажет. Установленный программным путем бит EEMWE аппаратно очищается через четыре тактовых цикла.

0 Бит 1 - EEWE (EEPROM Write Enable) - разрешение записи EEPROM. Сигнал разрешения записи EEPROM EEWE является стробом записи в EEPROM. Запись установленных данных по установленному адресу EEPROM выполняется по установке бита EEWE. При этом бит EEMWE обязательно должен быть в состоянии 1, иначе запись не произойдет. Процесс записи EEPROM выполняется следующей процедурой (очередность выполнения пунктов 2 и 3 значения не имеет):

Подождать сброса бита EEWE в состояние 0.

Записать новый адрес в EEAR (при необходимости).

Записать новые данные (при необходимости).

Установить в состояние 1 бит EEMWE регистра EECR.

В течение четырех тактовых циклов после установки EEMWE

установить в состояние 1 бит EEWE.

По истечении времени записи (типовое значение 2,5 мс при напряжении питания Vcc = 5 В) бит EEWE аппаратно очищается. Пользовательское программное обеспечение может тестировать состояние этого бита для определения момента сброса его в 0, чтобы начать запись следующего байта. После установки бита EEWE процессорное ядро, прежде чем начать выполнение следующей команды, останавливается на два тактовых цикла.

0 Бит 0 - EERE (EEPROM Read Enable) - разрешение чтения EEPROM. Сигнал разрешения чтения EERE является стробом чтения EEPROM. Бит EERE должен быть установлен после записи в регистр EEAR требуемого адреса. После аппаратной очистки бита EERE считываемые данные будут располагаться в регистре EEDR. Считывание байта данных выполняется одной командой и не требует опроса бита EERE. При установленном бите EERE CPU останавливается на четыре тактовых цикла, прежде чем начнет выполнение следующей команды. Пользователю необходимо тестировать состояние бита EEWE перед началом операции чтения. Если новые данные или адрес будут записываться в регистры ввода/вывода EEPROM в то время, когда будет выполняться операция записи, то операция записи будет прервана и результат записи будет неопределенным.

Содержимое EEPROM может быть разрушено при снижении напряжения питания Vcc до уровня, при котором процессорное ядро и EEPROM работают неправильно.

Разрушение данных EEPROM происходит по двум причинам. Во-первых, для правильного выполнения операций записи необходимо, чтобы напряжение питания было не ниже определенного. Во-вторых, само ядро при слишком низком напряжении питания может неправильно выполнять команды.

Разрушения данных можно предотвратить при следующих условиях:

0 Во время снижения напряжения питания аппаратно удерживать сигнал сброса #RESET в активном (низком) состоянии.

0 В период снижения напряжения питания переводить ядро микроконтроллера в режиме пониженного энергопотребления (Power Down Sleep).

0 Сохранять константы в Flash-памяти программ, если нет необходимости изменять их программно. Flash память не изменяется процессорным ядром и, следовательно, не может быть повреждена.