Управление аналого-цифровым преобразователем

В состав микроконтроллеров обычно включают 8 - 16-битные многоканальные преобразователи с большим набором встроенных функций. При этом все функции преобразователя программируются и могут быть изменены в процессе работы.

Например, микроконтроллер ATmega163 оснащен 10-разрядным ADC последовательных приближений (рис. 10.6). ADC подсоединен к 10-канальному аналоговому мультиплексору (MUX), позволяющему подать на вход преобразователя любой из восьми входных сигналов со входов ADC0…. ADC7, либо эталонное напряжение 1,22В, либо сигнал со входа AGND. Вывод AGND рекомендуется подсоединить к точке c нулевым потенциалом GND (Ground). ADC содержит схему выборки/хранения SHC (Sample&Hold Comparator), удерживающую напряжение входа во время преобразования на неизменном уровне.

|

Рис. 10.6. Структура аналого-цифрового преобразователя

Аналого-цифровой преобразователь преобразует напряжение аналогового входного сигнала в 10-разрядное цифровое значение методом последовательных приближений. Минимальное значение входного напряжения равно напряжению на контакте AGND, максимальное значение не должно превышать напряжение на контакте AREF. Результат в виде 10-битного двоичного числа D равен:

где U- входное напряжение, a Uo опорное напряжение преобразователя.

В качестве источника опорного напряжения преобразователя можно использовать внешний сигнал с вывода AREF, внутренний источник 2,56В, либо напряжение питания аналоговой части микроконтроллера с вывода AVCC. Напряжение на выводе AVCC не должно отличаться от напряжения питания Vcc более, чем на ±0,3 В.

Например, если аналоговый мультиплексор подключает ко входу ADC эталонное напряжение U =1,22В, а в качестве опорного напряжения использовать источник Uo=2,56B, то результат преобразования:

D=1,22*1024/2,56=488=$1E8=Ob111101000.

Для управления преобразователем в микроконтроллере используются регистры:

0 Регистр управления мультиплексором ADMUX (ADC Multiplexer Selection Register);

0 Регистр управления аналого-цифровым преобразователем ADCSR (ADC Control and Status Register)

0 Регистры данных ADCL и ADCH (ADC Low и ADC High).

0 Регистр состояния микроконтроллера SREG (Status Register).

|

Рис. 10.7. Регистры, используемые аналого-цифровым преобразователем

Аналого-цифровой преобразователь может работать в двух режимах: режиме однократного преобразования и в циклическом режиме. В режиме однократного преобразования каждое преобразование инициируется пользователем. В циклическом режиме аналого-цифровой преобразователь осуществляет выборку и обновление содержимого регистра данных непрерывно. Выбор режима производится битом ADFR ((ADC Free Run) регистра ADCSR.

Работа аналого-цифрового преобразователя разрешается установкой в состояние 1 бита ADEN в регистре ADCSR. Преобразование начинается с установки в состояние 1 бита начала преобразования ADSC (ADC Start Conversion). Если в процессе выполнения преобразования производится смена канала данных, то ADC вначале закончит текущее преобразование, а потом выполнит переход к другому каналу.

Поскольку аналого-цифровой преобразователь формирует 10-разрядный результат, то по завершении преобразования результирующие данные размещаются в двух регистрах данных ADCH и ADCL. Для обеспечения соответствия результирующих данных считываемому уровню используется специальная лотка защиты. Этот механизм работает следующим образом: при считывании данных первым должен быть считан регистр ADCL. Если регистр ADCL считан, обращение аналого-цифрового преобразователя к регистрам данных блокируется. Таким образом, если после считывания состояния ADCL, но до считывания ADCH, будет завершено следующее преобразование, ни один из регистров не будет обновлен и записанный ранее результат не будет искажен. Обращение аналого-цифрового преобразователя к регистрам ADCH и ADCL разрешается по завершении считывания содержимого регистра ADCH.

Аналого-цифровой преобразователь имеет свое собственное прерывание ADC (вектор $1С), которое может быть активизировано по завершению преобразования. Когда обращение к регистрам запрещено, в процессе считывания регистров ADCL и ADCH, прерывание будет активизироваться, даже при потере результата.

Регистр ADMUX (ADC Multiplexer Selection Register) предназначен для управления входным аналоговым мультиплексором

0 Биты 7 и 6 - REFS1..0 (Reference Selection Bits) - обеспечивают выбор эталонного напряжения на входе AREF аналого-цифрового преобразователя. Выбор производится в соответствии с таблицей 10.1. Изменение этих битов во время процесса преобразования приводит к ошибке. Для её исключения пользователь должен игнорировать первый результат после изменения битов. Внутренние источники напряжения не могут быть использованы, если к контакту AREF приложено внешнее напряжение.

Таблица 10.1. Выбор источника опорного напряжения аналого-цифрового преобразователя

| REFS1 | REFS0 | Выбор источника напряжения |

| AREF, внутреннее напряжение Vref отключено | ||

| AVCC с внешним конденсатором на контакте AREF | ||

| Резерв | ||

| Внутренний источник 2.56В с внешним конденсатором на AREF |

0 Бит 5 - ADLAR (ADC Left Adjust Result) - воздействует на запись результата в регистры данных ADCL и ADCH. При ADLAR=0 можно использовать упрощенное 8-битное преобразование.

0 Биты 4..0 - MUX4..MUX0 (Multiplexer bits) - предназначены для выбора входа, коммутируемого на вход преобразователя. Выбор осуществляется в соответствии с таблицей 10.2. Изменение этих битов в процессе преобразования, когда флаг ADIF в регистре ADCSR установлен, не приводит к изменению результата.

Таблица 10.2. Выбор входного сигнала ADC

| MUX4..0 | Подключаемый контакт |

| ADC0 | |

| ADC1 | |

| ADC2 | |

| ADC3 | |

| ADC4 | |

| ADC5 | |

| ADC6 | |

| ADC7 | |

| 01000. .11101 | Резерв |

| 1.22V | |

| 0V (AGND) |

Регистр - ADCSR (ADC Control and Status Register) предназначен для управления работой аналого-цифрового преобразователя.

0 Бит 7 - ADEN (ADC Enable) - разрешение работы ADC. Очистка бита запрещает работу ADC. Запрещение ADC в процессе преобразования прекращает преобразование.

0 Бит 6 - ADSC (ADC Start Conversion) - запуск преобразования ADC. В режиме однократного преобразования для запуска каждого цикла преобразования необходимо устанавливать бит ADSC в состояние 1. В циклическом режиме бит ADSC устанавливается в состояние 1 только при запуске первого цикла преобразования. Каждый раз после первой установки бита ADSC, выполненной после разрешения или одновременно с разрешением, будет выполняться пустое преобразование. Это пустое преобразование активизирует преобразователь. ADSC будет сохранять состояние 1 в течение всего цикла преобразования и сбрасывается по его завершению. При выполнении пустого преобразования, предшествующего активизируемому, бит ADSC остается установленным до завершения активируемого преобразования. Запись 0 в этот бит эффекта не оказывает.

0 Бит 5 - ADFR (ADC Free Run Select) - установка циклического режима работы ADC. При установленном в состояние 1 бите ADFR аналого- цифровой преобразователь будет работать в циклическом режиме. В этом режиме производятся выборки и обращения к регистрам непрерывно (одно за другим). Очистка бита приводит к прекращению циклического режима.

0 Бит 4 - ADIF (ADC Interrupt Flag) - флаг прерывания ADC. Данный бит устанавливается в состояние 1 по завершению преобразования и обновления регистров данных. Прерывание по завершению преобразования ADC выполняется, если в состояние 1 установлены бит ADIE и I - бит регистра статуса SREG. Бит ADIF сбрасывается аппаратно при выполнении подпрограммы обработки соответствующего вектора прерывания. Кроме того, бит ADIF может быть очищен записью во флаг логической 1. Этого необходимо остерегаться при чтении-модификации-записи ADCSR, поскольку может быть запрещено отложенное прерывание. Это применимо и в случаях использования команд sbi и cbi.

0 Бит 3 - ADIE (ADC Interrupt Enable) - разрешение прерывания ADC. При установленных в состояние 1 бите ADIE и l-бите регистра SREG активируется прерывание с вектором $1С по завершению преобразования ADC.

0 Биты 2..0 - ADPS2..ADPS0 (ADC Prescaler Select Bits) - выбор коэффициента предварительного деления. Данные биты определяют коэффициент деления тактовой частоты микроконтроллера для получения необходимой тактовой частоты ADC.

Таблица 10.3. Выбор коэффициента предварительного деления

| ADPS2 | ADPS1 | ADPS0 | Коэффициент деления |

| Без деления | |||

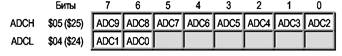

Регистры ADCL и ADCH являются регистрами данных. Их содержимое зависит от состояния бита ADLAR регистра ADMUX.

Когда преобразование выполнено десятибитный результат находится в этих двух регистрах. Если младший регистр ADCL считан, то регистры не изменяются до чтения старшего регистра ADCH. ADLAR бит в ADMUX воздействует на представление результата. Если ADLAR сброшен, то результат представлен в виде, изображенном на рис. 10.8.

|

Рис. 10.8. Представление результата в регистре данных при ADLAR=0

Если достаточным является 8-битное преобразование, то при ADLAR=0 можно считывать только старший байт результата (регистр ADCH).