рефераты конспекты курсовые дипломные лекции шпоры

- Раздел Высокие технологии

- /

- Интерфейс SPI

Реферат Курсовая Конспект

Интерфейс SPI

Интерфейс SPI - раздел Высокие технологии, АРХИТЕКТУРА МИКРОКОНТРОЛЛЕРА Последовательный Периферийный Интерфейс Spi (Serial Periph...

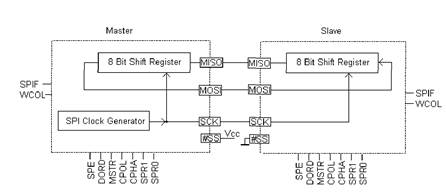

Последовательный периферийный интерфейс SPI (Serial Peripheral Interface) предложен фирмой Motorola. Он обеспечивает полный дуплексный обмен данными между двумя контроллерами. При этом один контроллер считается ведущим (master), второй - ведомым (slave). Ведущий контроллер является источником сигнал синхронизации (SCK) (рис. 13.6).

|

Рис. 13.6. Соединение устройств с интерфейсом SPI Ведущий и ведомый контроллеры связаны тремя сигнальными линиями:

0 MISO (Master In Slave Out) - вход ведущего - выход ведомого,

0 MOSI (Master Out Slave In) - выход ведущего - вход ведомого,

0 SCK (Serial Clock) - синхронизация,

Контакт #SS (Slave Select) - предназначен для выбора ведомого контроллера. Контроллер является ведомым при #SS = 0.

Регистры сдвига (Shift Register) ведущего и ведомого контроллеров по линиям MOSI и MOSO соединяются в кольцо. Запись в регистр данных ведущего контроллера запускает генератор синхронизации (SPI clock generator) и данные сдвигаются в регистрах сдвига соединенных в кольцо ведущего и ведомого контроллеров.

При восьмибитных регистрах обмен длится 8 тактов. По окончании обмена генератор синхронизации останавливается и устанавливается флаг окончания передачи. Если в контроллере разрешены прерывания (бит SPIE в регистре SPCR установлен) прерывание регистрируется.

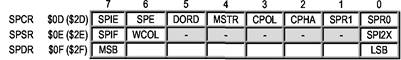

Управление SPI осуществляется через регистры ввода/вывода. В контроллере ATmega 163 такими регистрами являются:

0 Регистр SPCR (SPI Control Register) - регистр управления SPI,

0 Регистр SPSR (SPI Status Register) - регистр статуса SPI,

0 Регистр SPDR (SPI Data Register) - регистр данных SPI

|

Рис. 13.7. Регистры SPI

Регистр данных SPDR доступен для записи и чтения. Запись в регистр инициализирует передачу данных. Чтение регистра позволяет получить результат обмена.

Регистр управления SPI содержит биты управления передачей данных.

0 Бит 7 - SPIE (SPI Interrupt Enable) - бит маски прерывания SPI. Если бит SPIE установлен и установлен также бит I глобального разрешения прерывания в регистре статуса SREG, то прерывание разрешается.

0 Бит 6 - SPE (SPI Enable) - бит разрешения работы SPI. Если бит SPE установлен, то SPI включен.

0 Бит 5 - DORD (Data Order) - порядок передачи данных. Если бит DORD установлен, то младший бит данных (LSB) передается первым. Если бит DORD сброшен - первым передается старший бит данных (MSB).

0 Бит 4 - MSTR (Master/Slave Select) - выбор ведущего/ведомого. При установке этого бита выбирается режим ведущий/ведомый. Бит устанавливается, если контроллер является ведущим и сбрасывается, если - ведомым. Если на контакт #SS подан 0, в то время как бит MSTR установлен, то бит MSTR будет очищен, и установится флаг прерывания (бит SPIF в SPSR). Пользователь в этом случае может вновь установить бит MSTR и сделать контроллер ведущим.

0 Бит 3 - CPOL (Clock Polarity) - полярность сигнала синхронизации. Если бит CPOL установлен, то в SCK = 1 при отсутствии передачи.

0 Бит 2 - CPHA (Clock Phase) - фаза синхронизации. Синхронизация осуществляется по переднему фронту сигнала, если бит CPHA установлен, и по заднему -если бит CPHA сброшен.

0 Биты 1,0 - SPR1, SPR0 (SPI Clock Rate Select 1 and 0). Выбор частоты синхронизации. SPI синхронизируется от тактового генератора процессорного ядра ведущего контроллера СК. Частота передачи может быть изменена битами SPI2X регистра SPSR и SPR1 и SPR0 регистра SPCR в соответствии с таблицей 13.2. Для ведомого контроллера эти биты не существенны.

Таблица 13.2. Частота синхронизации SPI

| SPI2X | SPR1 | SPR0 | Частота | SPI2X | SPR1 | SPR0 | Частота |

| СК/4 | CK/2 | ||||||

| СК/16 | CK/8 | ||||||

| CK/64 | CK/32 | ||||||

| CK/128 | CK/64 |

В регистре SPSR хранятся флаги прерываний и ошибок SPI.

0 Бит 7 - SPIF (SPI Interrupt Flag) - флаг прерывания SPI. Бит устанавливается аппаратно при завершении передачи байта в SPI. Прерывание происходит, если установлен бит маски SPIE в регистре SPCR и прерывания глобально разрешены. Бит SPIF аппаратно сбрасывается при переходе по вектору прерывания.

0 Бит 6 - WCOL (Write Collision Flag) - флаг ошибки. Бит WCOL устанавливается, если данные в регистр SPDR записываются во время процесса передачи. Бит WCOL, как и бит SPIF, сбрасывается при первом чтении регистра статуса SPSR после обращения к регистру данных SPDR.

0 Бит 0 - SPI2X (Double SPI Speed Bit) - бит удвоения скорости передачи. Этот бит позволяет удвоить скорость передачи данных, как показано в таблице 13.2

13.3. Интерфейс I2 C

2-проводной последовательный интерфейс (2-Wire Serial Interface) или I С (Inter- Integrated Circuit) предложен фирмой Philips. Он поддерживает двунаправленную последовательную связь нескольких устройств в полудуплексном режиме.

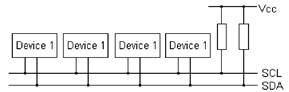

В системе все устройства, участвующие в обмене, связываются двумя сигнальными линиями:

0 SDA (Serial Data) -данные,

0 SCA (Serial Clock) - синхронизация.

На рис. 13.8 показана типичная 2-проводная последовательная конфигурация шины.

|

Рис.13.8. Соединение устройств с интерфейсом I 2C.

Каждое из устройств может выступать в роли передатчика или приемника. Синхронизацию обмена обеспечивает передатчик. Двунаправленную линию данных, выполненную по схеме «открытый коллектор» используют передатчик и приемник поочередно. Частота обмена ограничена сверху величиной 100 кГц для стандартного режима и 400 кГц - для скоростного. Протокол обмена иллюстрируется рис. 13.9.

|

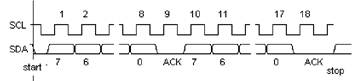

Рис. 13.9. Протокол передачи данных интерфейса I 2

Начало любой операции (Start) инициализируется переводом сигнала SDA из высокого уровня в низкий при высоком уровне SCL. Завершается обмен переводом сигнала SDA из низкого уровня в высокий при высоком уровне SCL (Stop).

При передаче данных состояние линии SDA может изменяться только при низком уровне SCL. Биты данных стробируются положительным фронтом SCL.

Каждая посылка, формируемая передатчиком, состоит из байта данных. Посылка начинается со старшего бита. После чего передатчик на один такт освобождает линию, а приемник формирует нулевой сигнал подтверждения Ack (Acknowledge).

Каждое ведомое устройство имеет свой 7-битный адрес. Семь бит адреса передаются ведущим устройством в битах [7-1] первого байта, бит 0 содержит признак операции R/W (Read/Write):

0 R/W =0 - запись,

0 R/W =1 - чтение.

Старшие четыре бита адреса несут информацию о типе устройства (например, для EEPROM - 1010), а младшие три - номер устройства данного типа. К одной шине допускается подключение до восьми однотипных устройств.

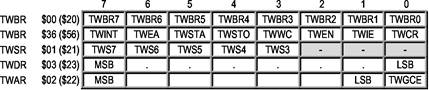

Для управления TWSI используются регистры:

0 Регистр задания скорости передачи TWBR (Two wire Serial Interface Bit Rate Register);

0 Регистр управления TWCR (2-wire Serial Interface Control Register);

0 Регистр статуса TWSR (2-wire Serial Interface Status Register);

0 Регистр данных TWDR (2-wire Serial Interface Data Register);

0 Регистр адреса (ведомого) TWAR (2-wire Serial Interface (Slave) Address Register).

|

Рис. 13.10. Регистры TWSI

Регистр данных TWDR (2-Wire Serial Interface Data Reg ) хранит байт данных, для передачи или последний байт данных, полученный на 2-проводной последовательной шине.

Регистр - TWAR (2-wire Serial Interface (Slave) Address Register) хранит 7-битный адрес устройства на двухпроводной последовательной шине.

0 Бит 0 - TWGCE (2-wire Serial Interface General Call Recognition Enable bit) - бит распознавания запроса. При установке бита выполняется операция чтения, при сбросе - операция записи.

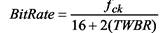

Ретстр TWBR (2-wire Serial Interface Bit Rate Register) предназначен для задания скорости передачи данных. Частота синхронизации связана с содержимым регистра соотношением:

|

0 Bit Rate - частота SCL

0 fck - тактовая частота ядра

Ретстр TWCR предназначен для управления передачей данных.

0 Бит 7 - TWINT (2-wire Serial Interface Interrupt Flag) - флаг прерывания 2-х проводного интерфейса. Бит устанавливается аппаратно, когда 2-проводной последовательный интерфейс закончил выполнение текущего задания и находится в состоянии ожидания. Если бит I в регистре статуса SREG установлен и установлен также бит TWIE в регистре TWCR, то происходит переход на вектор прерывания TWSI с адресом $022. Флажок TWINT должен быть очищен программно.

0 Бит 6 - TWEA (2-wire Serial Interface Enable Acknowledge Flag) - флаг разрешения подтверждения. Если флаг установлен, то сигнал подтверждения ACK генерируется при следующих условиях: Устройством получен его адрес, Общий запрос был получен, в то время как TWGCE бит в регистре TWAR установлен. Байт данных был получен в главном приемнике или подчиненном режиме приемника.

Если бит TWEA сброшен, устройство фактически разъединено с 2- проводной последовательной шиной. При повторной установке бита TWEA распознавание адреса возобновляется.

0 Бит 5 - TWSTA (2-wire Serial Bus START Condition Flag) - флаг разрешения старта. Флаг TWSTA устанавливается, если устройство объявляется ведущим (мастером) на двухпроводной шине. Двухпроводной интерфейс аппаратно проверяет шину и разрешает установку бита, только если шина свободна. Если шина занята, интерфейс ждет конца передачи.

0 Бит 4 - TWSTO (2-wire Serial Bus STOP Condition Flag) - флаг остановки. Если контроллер ведущий, бит TWSTO устанавливается для остановки передачи на линии. Когда условие остановки выполнено, бит TWSTO аппаратно очищается.

0 Бит 3 - TWWC (2-wire Serial Bus Write Collision Flag) - флаг ошибки передачи. Бит TWWC устанавливается в случае попытки записи в регистр данных интерфейса при сброшенном бите TWINT. Этот флажок очищается при установке бита TWINT.

0 Бит 2 - TWEN (2-wire Serial Interface Enable Bit). - флаг включения двухпроводного интерфейса. Бит TWEN включает двухпроводной интерфейс. Если бит сброшен, шины выводы SDA и SCL контроллера переводятся в высокоимпедансное состояние.

0 Бит 0 - TWIE (2-wire Serial Interface Interrupt Enable) - бит маски прерывания. Если бит установлен и установлен бит I в регистре статуса SREG, то при установке флага TWINT происходит прерывание.

Регистр TWSR доступен только для чтения.

0 Биты 7..3 - TWS (2-wire Serial Interface Status). Эти 5 битов отражают состояние логики последовательного интерфейса и 2-проводной последовательной шины. Код состояния доступен в регистре TWSR в течении одного тактового цикла после прерывания от интерфейса. Специальные таблицы позволяют определить состояние интерфейса при различных кодах состояния.

– Конец работы –

Эта тема принадлежит разделу:

АРХИТЕКТУРА МИКРОКОНТРОЛЛЕРА

Создание фирмой Intel в году первой программируемой электронной схемы на... За лет своего бурного развития микропроцессорные системы прошли путь от специализированных комплектов интегральных...

Если Вам нужно дополнительный материал на эту тему, или Вы не нашли то, что искали, рекомендуем воспользоваться поиском по нашей базе работ: Интерфейс SPI

Что будем делать с полученным материалом:

Если этот материал оказался полезным ля Вас, Вы можете сохранить его на свою страничку в социальных сетях:

| Твитнуть |

Хотите получать на электронную почту самые свежие новости?

Новости и инфо для студентов