Организация памяти.

В микроконтроллерах AVR семейства MEGA реализована Гарвардская архитектура, в соответствии с которой разделены не только адресные пространства памяти программ и памяти данных, но также и шины доступа к ним. Каждая из областей памяти данных (ОЗУ и EEPROM) также расположены в своем адресном пространстве.

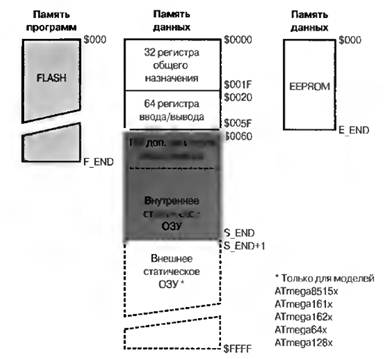

Карта памяти представлена на рисунке

Память программ предназначена для хранения команд, управляющих функционированием микроконтроллера. Память программ может использоваться для хранения констант, не меняющихся во время работы программы.

Память программ имеет 16-разрядную организацию. Объем составляет от 4к до 64к 16-разрядных слов.

Для адресации памяти программ используется счетчик команд (PC – Program Counter). Размер счетчика команд составляет от 12 – 16 разрядов в зависимости от объема адресуемой памяти.

По адресу $0000 памяти программ находится вектор сброса. После инициализации (сброса) микроконтроллера выполнение программы начинается с этого адреса (по этому адресу должна размещаться команда перехода к инициализационной части программы).

Начиная с адреса $0001 (для Mega8x Mega8515x) или $0002 (остальные модели) памяти программ, располагается таблица векторов прерываний.

При возникновении прерывания после сохранения в стеке текущего значения счетчика команд происходит выполнение команды расположенной по адресу соответствующего вектора прерывания. Поэтому по этим адресам располагаются команды перехода к подпрограммам обработки прерываний

Память данныхразделена на три части: регистровая память, оперативная память (статическое ОЗУ) и энергонезависимое ЭСППЗУ (EEPROM).

Регистровая память включает 32 регистра общего назначения (РОН), объединенных в файл, и служебные регистры ввода/вывода (РВВ). В моделях Mega162 Mega64 Mega128 имеется область дополнительных регистров ввода/вывода.

Объем статического ОЗУ составляет 512 байт – 4кбайт. В адресном пространстве ОЗУ также расположены все регистры микроконтроллеров.

Регистры общего назначенияобъединены в регистровый файл быстрого доступа. Все 32 регистра РОН непосредственно доступны АЛУ, что позволяет в сочетании с конвееризацией выполнять команду за один машинный цикл.

Регистры X Y Z используются в качестве указателей при косвенной адресации памяти данных. К этим регистрам можно обращаться и как к регистрам и как к ячейкам памяти данных.

Регистры ввода/выводаусловно можно разделить на две группы: служебные регистры микроконтроллера, регистры относящиеся к конкретным периферийным устройствам.

Важный регистр микроконтроллера – регистр состояния (SREG). Он содержит набор флагов, показывающих текущее состояние микроконтроллера.