рефераты конспекты курсовые дипломные лекции шпоры

- Раздел Транспорт

- /

- Иерархические блоки

Реферат Курсовая Конспект

Иерархические блоки

Иерархические блоки - раздел Транспорт, АВТОМАТИЗИРОВАННОЕ ПРОЕКТИРОВАНИЕ СЛОЖНЫХ СИСТЕМ Любой Фрагмент Схемы Можно Оформить В Виде Иерархического Блока, Символ Котор...

Любой фрагмент схемы можно оформить в виде иерархического блока, символ которого представляет собой прямоугольник, и затем разместить его на схеме, что позволяет уменьшить ее размеры. Другое применение иерархических блоков — представление с их помощью повторяющихся фрагментов схем: различных фильтров, усилителей, выпрямителей, сумматоров и т.п.

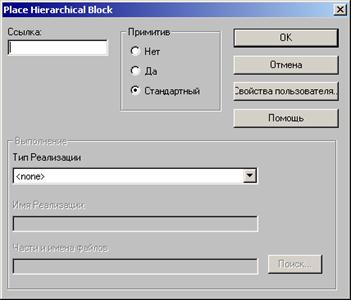

Иерархический блок размещается на схеме по команде Place>Hierarchical Blockили нажатием на кнопку  панели инструментов. На следующем рисунке представлено диалоговое окно этой команды.

панели инструментов. На следующем рисунке представлено диалоговое окно этой команды.

Диалоговое окно, показанное на рисунке, имеет следующие панели:

Ø Ссылка — позиционное обозначение иерархического блока;

Ø Тип реализации — тип иерархического блока, принимающий значения:

o Схемы — схема объекта,

o VHDL — описание компонента на языке VHDL,

o EDIF — список соединений в формате EDIF,

o Project — проект ПЛИС,

o PSpice Model — файл математической модели в формате PSpice; причем в этом блоке необходимо вручную разместить иерархические выводы,

o PSpice Stimulus — файл внешнего воздействия в формате PSpice; причем в этом блоке необходимо вручную разместить иерархические выводы;

Ø Имя реализации – имя иерархического блока;

Ø Части и имена файлов – полное имя файла, в котором находится описание иерархического блока (не указывается, если файл размещается в каталоге текущего проекта, в этом случае в качестве имени его папки принимается имя иерархического блока);

Ø Примитив – тип блока: Да – элементарный блок; Нет – блок, имеющий иерархическую структуру, Стандартный – устанавливается по умолчанию (в соответствием с настройкой конфигурации на закладке Hierarchy команды Options>Design Template;

Ø Свойства пользователя — открытие диалогового окна для ввода дополнительных параметров блока.

Для включения в схему устройства заранее спроектированного модуля, необходимо в качестве типа реализации выбрать "Схемы", а в качестве имени реализации ввести тот раздел "Schematic" проекта, который содержит реализованный модуль. После этого, при размещении иерархического блока на рабочем пространстве, автоматически на нем будут обозначены входные и выходные контакты, соответствующие входным и выходным портам модуля.

Если схемы замещения нет, то после закрытия диалогового окна и размещения иерархического блока, по команде Place>Hierarchical Pinили нажатием на кнопку  панели инструментов вводятся выводы этого блока Диалоговое окно команды приведено на следующем рисунке:

панели инструментов вводятся выводы этого блока Диалоговое окно команды приведено на следующем рисунке:

В диалоговом окне указываются:

Ø на панели Name — имя вывода;

Ø в графе Туре — тип вывода:

o 3 State — вывод цифрового компонента, имеющий три состояния;

o Bidirectional — двунаправленный вывод цифрового компонента;

o Input — вход;

o Open Collector — вывод цифрового компонента типа открытый коллектор!

o Open Emitter — вывод цифрового компонента типа открытый эмиттер!

o Output — выход;

o Passive — вывод пассивного компонента;

o Power — вывод подключения к источнику питания;

Ø на панели Width выбирается тип цепи, подключаемой к выводу:

o Scalar — одиночная цепь;

o Bus — шина.

Чтобы не открывать это окно каждый раз при размещении нового вывода, можно разместить все выводы блока одного типа, а затем отредактировать таблицу всех выводов, выбрав строку Edit Propertiesво всплывающем меню.

После завершения команды Place>Hierarchical Blockавтоматически создается папка с указанным именем. В эту папку необходимо поместить описание иерархического блока в виде его схемы замещения (если выбран тип блока Schematic View) или текстового описания на языке VHDL. Цепям, которые подключаются к выводам иерархического блока, присваиваются имена, совпадающие с именами соответствующих выводов, или по команде Place>Hierarchical Portили нажатием на кнопку панели инструментов вводятся внешние порты схемы этого блока (имена портов также должны совпадать с именами соответствующих выводов, чтобы обеспечить их электрическое соединение).

– Конец работы –

Эта тема принадлежит разделу:

АВТОМАТИЗИРОВАННОЕ ПРОЕКТИРОВАНИЕ СЛОЖНЫХ СИСТЕМ

НАЦИОНАЛЬНЫЙ ТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ... quot ХАРЬКОВСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ quot Леонов С Ю Гладких Т В...

Если Вам нужно дополнительный материал на эту тему, или Вы не нашли то, что искали, рекомендуем воспользоваться поиском по нашей базе работ: Иерархические блоки

Что будем делать с полученным материалом:

Если этот материал оказался полезным ля Вас, Вы можете сохранить его на свою страничку в социальных сетях:

| Твитнуть |

Хотите получать на электронную почту самые свежие новости?

Новости и инфо для студентов