Методичні вказівки з курсу Автоматизація проектування комп’ютерних систем

МІНІСТЕРСТВО ОСВІТИ І НАУКИ УКРАЇНИ

УЖГОРОДСЬКИЙ НАЦІОНАЛЬНИЙ УНІВЕРСИТЕТ

ІНЖЕНЕРНО-ТЕХНІЧНИЙ ФАКУЛЬТЕТ

КАФЕДРА « КОМП’ЮТЕРНИХ СИСТЕМ ТА МЕРЕЖ»

МОВА ОПИСУ АПАРАТУРИ AHDL

Методичні вказівки з курсу

Автоматизація проектування комп’ютерних систем

Частина 1

ОСНОВИ МОВИ AHDL

Ужгород 2008

«Автоматизація проектування комп’ютерних систем» для студентів 4-го курсу інженерно-технічного факультету спеціальність «Комп’ютерні системи та мережі»ВСТУП

Мова AlteraHDL (AHDL) - мова опису апаратури, створена фірмою Altera в 1983 році. До теперішнього часу, пройшовши довгий шлях розвитку, вона являє собою ефективний засіб для:

■ поведінкового й структурного опису проектованого пристрою;

■ документування проекту.

Система синтезу пакета MAX+plus II, у який мова AHDL інтегрована, забезпечує його архітектурну незалежність: текстовий опис може бути без переробки синтезовано на базі будь-якої НВІС (Над Великої Інтегральної Схеми) програмувальної логіки, включеної в пакет MAX+plus II.

На відміну від таких мов як VHDL і VerilogHDL, орієнтованих на опис і моделювання системи (наприклад: процессор-память-проектований пристрій), мова AHDL більш проста у вивченні й оптимізована по своїх можливостях для проектування окремої НВІС. Однак, незважаючи на свою відносну простоту, вона містить типовий для сучасних мов опису апаратури набір високорівневих конструкції.

Проект

Під терміном «проект» у рамках пакета MAX+plus II розуміють набір файлів, пов'язаних із проектованим модулем, у якому виділяються дві групи файлів:

■ логічні файли, що описують алгоритм роботи пристрою (Design Files);

■ допоміжні файли(Ancilary Files).

Проект може містити один логічний файл або кілька логічних файлів, що утворять ієрархічний опис проектованого модуля. При ієрархічному описі серед безлічі логічних файлів розрізняють:

■ файл верхнього рівня в ієрархії описів (Top-level Design File);

■ файли нижніх (одного або декількох) рівнів ієрархії (Low-level Design files).

У файлі верхнього рівня задається архітектура модуля, визначається набір модулів, що входять до його складу як компоненти, і їхній взаємозв'язок. Опис цих модулів знаходиться в логічних файлах більш низького рівня ієрархії. У їхній склад, у свою чергу, у вигляді компонентів також можуть входити модулі, описи яких наведені в логічних файлах ще більш низького рівня ієрархії, і т.д.

Ім'я проекту повинно збігатися з ім'ям модуля верхнього рівня в ієрархії описів, а отже, і ім'ям логічного файлу, у якому зберігається його опис. Імена модулів нижніх рівнів ієрархії, у свою чергу, повинні збігатися з іменами файлів, у яких вони описані.

Логічний файл - це файл одного з наступних типів:

■ Graphic Design File – графічний файл (стандартне розширення - gdf). Файл містить схему, створену в рамках пакета MAX+plus II;

■ AHDL Text Design File – текстовий файл (стандартне розширення - .tdf). Файл містить текстовий опис модуля мовою AlteraHDL;

■ Waveform Design File – хвильовий файл (стандартне розширення - .wdf). Файл містить часові діаграми вхідних і вихідних сигналів, створених в рамках пакета MAX+plus II;

■ VHDL Design File – текстовий файл (стандартне розширення - .vdf). Файл містить текстовий опис модуля мовою VHDL;

■ Verilog Design File – текстовий файл (стандартне розширення - .v).

Файл містить текстовий опис модуля мовою Verilog HDL;

■ Orcad Schematic Files – схемний файл (стандартне розширення –

.sch).Файл містить схему, створену в рамках пакета ORCAD;

■ EDIF Input Files (стандартне розширення - . edf). Файл містить опис у форматі EDIF 200 або 300;

■ Xilinx Netlist Format File (стандартне розширення - . xnf). Файл містить опис модуля, отриманого в рамках пакета фірми Xilinx.

Допоміжні файли зберігають додаткову інформацію про проект. Їхні імена збігаються з ім'ям проекту.

1. ЕЛЕМЕНТИ МОВИ

1.1. Ключові слова й ідентифікатори

Повний перелік ключових слів (Keywords) і ідентифікаторів (Identifires) мови AHDL наведений у табл. 1 і табл. 2 відповідно.

Таблиця 1. Ключові слова

| AND ASSERT BEGIN BIDIR BITS BURIED CASE CLIQUE CONNECTED PINS CONSTANT DEFAULTS DEFINE DESIGN DEVICE DIV ELSE ELSIF END FOR | FUNCTION GENERATE GND HELP_ID IF INCLUDE INPUT IS LOG2 MACHINE MOD NAND NODE NOR NOT OF OPTIONS OR OTHERS | OUTPUT PARAMETERS REPORT RETURNS SEGMENTS SEVERITY STATES SUBDESIGN TABLE THEN TITLE TO TRI_STATE_NODE VARIABLE VCC WHEN WITH XNOR XOR |

Таблиця 2. Ідентифікатори

| CARRY CASCADE CEIL DFFE DFF EXP FLOOR GLOBAL | JKFFE JKFF LATCH MSELL MEMORY OPENDRN SOFT | SRFFE SRFF TFFE TFF TRI USED WIRE X |

Символи

Таблиця 3. Символи, використовувані в мові AHDL Символ Опис _ Підкреслення (Underscore) - Тире …Мена

У мові AHDL визначені три типи імен:

■ Символічне ім'я (Symbolic name)

■ Ім'я модуля (Subdesign name)

■ Ім'я виводу (Port name).

Символічне ім'я — обумовлене користувачем ім'я, використовуване для задання:

■ змінних;

■ констант;

■ станів і розрядів скінченого автомата;

■ параметрів;

■ позначуваних арифметичних виразів;

■ іменованих операторів.

Ім'я модуля — обумовлене користувачем ім'я, використовуване для іменування модуля, а також логічного файлу, у якому зберігається його текстовий опис.

Ім'я виводу — обумовлене користувачем ім'я, використовуване для позначення:

■ входу модуля;

■ виходу модуля;

■ двонаправленого виводу модуля;

■ входу для імпортованого скінченого автомата;

■ виходу для експортованого скінченого автомата.

Ім'я може бути задане в одній із двох форм:

■ рядком символів (від 1 до 32 символів) - Unquoted name;

■ рядком символів (від 1 до 32 символів), укладеним в одинарні лапки - Quoted name.

Правила використання зазначених форм зведені в табл. 4.

Таблиця 4

| Quoted Subdesign Name | Unquoted Subdesign Name | Unquoted Symbolic Name | Quoted Symbolic Name | Unquoted Port Name | Quoted Port Name | |

| Символи A..Z | + | + | + | + | + | + |

| Символи a..z | + | + | + | + | + | + |

| Цифри 0..9 | + | + | + | + | + | + |

| Підкреслення (_) | + | + | + | + | + | + |

| Коса риска (/) | + | + | + | + | ||

| Тире (-) | + | + | + | |||

| Тільки цифри 0..9) | + | + | + | + | + | |

| Ключове слово | + | + | + | |||

| Ідентифікатор | + | + | ||||

| Максимальне число символів |

Групи

Група - набір однотипних змінних або виводів. Порядковий номер змінної (виводу) у групі - індекс. Максимальне число змінних (виводів), об'єднаних в одну групу, не повинне перевищувати 256. У мові AHDL визначені три типи груп:

■ одновимірні (Single-range);

■ двовимірні (Dual-range);

■ послідовні (Sequential) або, що за змістом більш точно, часові.

Одновимірні групи задають, указуючи:

■ ім'я групи (символічне ім'я або ім'я виводу);

■ діапазон зміни індексів групи.

Двовимірні групи задають, указуючи:

■ ім'я групи (символічне ім'я або ім'я виводу);

■ пари діапазонів зміни індексів.

Послідовні (часові) групи задають списком, укладеним у круглі дужки. Елементами списку можуть бути змінні, виводи модуля, одновимірні групи, двовимірні групи. Елементи списку відділяються один від одного комами.

Індекси одновимірних і двовимірних груп повинні бути цілими додатними числами. Діапазон зміни індексів вказується в наступному форматі:

[ границя А.. границя В ].

Кожна із границь може бути визначена: числом, арифметичним виразом, константою або параметром.

Типовий порядок задання індексів - спадна зліва направо послідовність: границя А - більше ціле, границя В - менше. Якщо ж вони задані в зростаючій зліва направо послідовності або ж у рамках одного логічного файлу, використовуються обидва способи задання індексів, то рекомендується встановити опцію BITO=MSB або BITOANY відповідно. У протилежному випадку компілятор видасть попередження.

Приклади:

1. А[5. .0] - одновимірна група. Індекси задані спадною, зліва направо, послідовністю. Члени групи А5, А4, A3, А2, А1, А0.

2. CONSTANT UPPER=H"4"; B[UPPER..1] - одномірна група. Верхня границя діапазону зміни індексів визначена константою. Індекси задані спадною, зліва направо, послідовністю. Члени групи В4, ВЗ, В2, В1.

3. С[2*2. .0][3. .2] - двовимірна група. Верхня границя діапазону зміни першої групи індексів задана арифметичним виразом. Індекси задані спадною, зліва направо, послідовністю. Члени групи С43, С42, СЗЗ, С32, С23, С22, С13, С12, С0З, С02.

4. D[1..4] - одновимірна група. Індекси задані зростаючою зліва направо послідовністю. Члени групи: D1, D2, D3, D4.

5. (А, Е[2.. 1], F); - часова група. Члени групи: А, Е2, Е1, F.

Числа

Мова AHDL допускає можливість використання десяткових, двійкових, вісімкових та шістнадцяткових чисел. Правила задання чисел:

§ Десяткове число - сукупність цифр від 0 до 9.

§ Двійкове число - В "сукупність символів 0, 1, х", або b "сукупність символів 0, 1, х".

§ Вісімкове число - О "сукупність цифр від 0 до 7", або о "сукупність цифр від 0 до 7", або Q "сукупність цифр від 0 до 7", або q "сукупність цифр від 0 до 7".

§ Шістнадцяткове число - Н "сукупність цифр від 0 до 9 і букв від А до F", або h "сукупність цифр від 0 до 9 і букв від А до F", або X "сукупність цифр від 0 до 9 і букв від А до F", або х "сукупність цифр від 0 до 9 і букв від А до F".

Приклади:

В "10x01"; х "А1"; О"73".

Число не може бути присвоєно однорозрядній змінній або виходу. Замість числа варто використовувати константну одиницю (b”1” або VCC) або константний нуль (b"0", або GND).

Приклади:

1. out = b”1”; -- правильне присвоєння

2. out = 0; -- неправильне присвоєння

3. out = GND. -- правильне присвоєння.

Вирази

У мові AHDL визначені два типи виразів (Expressions):

■ Арифметичні вирази (Arithmetic Expressions);

■ Логічні вирази (Boolean Expressions).

1.6.1. Арифметичні вирази

Арифметичні вирази використовуються для задання:

■ позначуваного виразу в операторі позначення (Define Statement);

■ констант в операторі задання констант (Constant Statement);

■ границь діапазону зміни індексів одновимірних і двовимірних груп;

■ границь діапазону зміни внутрішньої змінної в операторі FOR GENERATE;

■ оцінюваного вирази в операторах IF GENERATE, ASSERT.

Приклади:

1. DEFINE Min (a,b) = ((a<b) ? a:b); -- ((a<b) ? a:b) - арифметичний вираз.

2. CONSTANT Const = 1+2DIV3+LOG2(256); -- 1+2DIV3+LOG2(256) – арифметичний вираз;

3. A[2+4^2..3-2] : INPUT; -- 2+4^2 і 3-2 – арифметичний вираз.

Значення арифметичних виразів оцінюється й підставляється компілятором на етапі перевірки синтаксису проекту і тому для реалізації не потрібні логічні ресурси НВІС ПЛ. У табл. 5 перераховані арифметичні, логічні оператори й оператори порівняння, які можуть використовуватися в арифметичних виразах Так само в табл. 5 зазначений пріоритет виконання операторів: чим менше число, тим вище пріоритет.

Результат арифметичного виразу повинен бути цілим додатним числом. У протилежному випадку він, за замовчуванням, округляється до найближчого більшого цілого.

Таблиця 5.

| Оператор | Приклад | Опис | Пріоритет виконання |

| + (unary) | +1 | Плюс | |

| -(unary) | -1 | мінус | |

| ! | !a | Заперечення | |

| ^ | a^2 | Степінь | |

| MOD | 4 MOD 2 | Модуль | |

| DIB | 4 DIV 2 | Ділення | |

| * | a*2 | Множення | |

| LOG2 | LOG(4-3) | Логарифм за основою 2 | |

| + | 1+1 | Додавання | |

| - | 1-1 | Віднімання | |

| = =(numeric) | 5= =5 | Рівність чисел | |

| = = (string) | “a”= = “b” | Рівність рядків | |

| != | 5!=4 | Не дорівнює | |

| > | 5>4 | Більше | |

| >= | 5>=5 | Більше або дорівнює | |

| < | a<b+2 | Менше | |

| <= | a<=b+2 | Менше або дорівнює | |

| & або AND | a&b або a AND b | І | |

| !& або NAND | 1 !& 0 або 1 NAND b | І-НІ | |

| $ або XOR | 1 $ 1 або 1 XOR 1 | Виключаюче АБО | |

| !$ або XNOR | 1 !$ 1 або 1 XNOR 1 | Виключаюче АБО-НІ | |

| # або OR | a # b або a OR b | АБО | |

| !# або NOR | a!# b або a NOR b | АБО-НІ | |

| ? | (5<4) ? 3:4 | Тернарна операція |

Крім того, у мові AHDL визначені дві функції, які можуть використовуватися в арифметичних виразах для явного задання правила округлення:

§ CEIL — округлення до найближчого більшого цілого;

§ FLOOR— округлення до найближчого меншого цілого.

Приклади:

1. CEIL (LOG2(255)) = 8.

2. FLOOR (5DIV3) = 1.

1.6.2. Логічні вирази

Логічні вирази (Boolean expressions) містять операнди, об’єднані:

§ логічними операторами;

§ арифметичними операторами;

§ операторами порівняння.

Логічні вирази використовуються:

§ у логічних рівняннях (Boolean Equations);

§ у логічних рівняннях, що задають керуючі сигнали (Boolean Control Equations);

§ в операторі CASE;

§ в операторі IF THEN.

Оператори

1.7.1. Логічні оператори

У таблиці. 2 перераховано логічні оператори, використовувані в логічних виразах.

Таблиця 6

| Оператор | Приклад | Опис |

| ! NOT | ! tob NOT tob | Інверсія |

| & AND | bread & butter bread AND butter | І |

| !& NAND | a[3..1] !& b[5..3] a[3..1] NAND b[5..3] | І-НІ |

| # OR | trick # treat trick OR treat | АБО |

| !# NOR | c[8..5] !# d[7..4] c[8..5] NOR d[7..4] | АБО-НІ |

| $ XOR | foo $ bar foo XOR bar | Виключаюче АБО |

| !$ XNOR | x2 !$ x4 x2 XNOR x4 | Виключаюче АБО-НІ |

Оператор інверсія (NOT) може застосовуватися до одного із трьох типів операндів:

■ Однорозрядної змінної (іменованої лінії зв'язку), однорозрядного виводу модуля, а також до константної логічної одиниці й константного логічного нуля. При цьому здійснюється інвертування аргументу операнда,

■ Групі змінних (групі іменованих ліній зв'язку), групі виводів модуля. У цьому випадку інвертується кожний член групи.

Приклад:

!(а, b[2..1]) відповідає !а, ! b2, !b1.

■ Числу. У цьому випадку інвертується кожний розряд двійкового еквівалента даного числа.

Приклад:

!9 = (!В"1001”=В"0110") = 6.

Оператори AND, NAND, OR, NOR, XOR, NXOR допускають використання наступних комбінацій операндів:

§ Обидва операнди однорозрядні: однорозрядна змінна, однорозрядний вивід модуля, логічний нуль або логічна одиниця.

§ Обидва операнди групи: група змінних або група виводів модуля. У цьому випадку логічний оператор застосовується порозрядно а, отже, операнди повинні мати однакове число розрядів, що збігається із числом розрядів результату.

Приклад:

R[4..1]=(A,B,C,D)#OP[3..0]; при цьому: R4=A#ОP3; R3=B#ОP2; R2=C#ОP1; R1=D#OP0;

§ Один операнд група (група змінних, група виводів модуля), а інший операнд однорозрядний (однорозрядна змінна, однорозрядний вивід модуля, логічний нуль, логічна одиниця). У цьому випадку однорозрядний операнд тиражується й формується група, число розрядів у якій дорівнює числу розрядів в іншому операнді. Потім до двох груп порозрядно застосовується логічний оператор.

Приклад:

R[3. . 1]=(а, b[2.. 1])&D; при цьому: R3=a&D; R2=b2&D; R1=b1&D.

§ Обидва операнди числа. Оскільки природною формою подання чисел для виконання процедури синтезу комбінаційної схеми є двійкова форма, то в цьому випадку обидва операнди розглядаються компілятором як двійкові числа (групи двійкових розрядів). Якщо для двійкового подання операндів потрібне різне число розрядів, то автоматично здійснюється нарощування числа розрядів двійкового подання меншого операнда. Логічний оператор застосовується до сформованих груп порозрядно.

Приклад:

3$14 = В"0011 $ В"1110"=В”1101”=13.

§ Один операнд число, а інший операнд або однорозрядний, або група. У цьому випадку число перетвориться у двійкове число (групу двійкових розрядів). Логічний оператор застосовується до цих груп порозрядно. Якщо число розрядів у цій групі менше числа розрядів в іншому операнді, то вона автоматично розширюється. Якщо ж більше, то процесор повідомлень (Message Processor) пакету MAX+plus II видає повідомлення про помилку.

Приклади:

R[3..1] = (a,b,c) & 3;

-- при цьому R3 = (a & B”0”) = 0; R[2] = (b&B"1")=b; R[1] = с&В”1" ) = с.

R[3. .1]=(a,b, с) & 9. -- при цьому буде сформоване повідомлення про помилку.

1.7.2. Арифметичні оператори

У табл. 7 перераховані арифметичні оператори, які можуть бути використані в логічних виразах.

У табл. 7 перераховані арифметичні оператори, які можуть бути використані в логічних виразах.

Таблиця 7.

| Оператор | Приклад | Опис |

| + (унарний) | +1 | Плюс |

| - (унарний) | -a[4..1] | Мінус |

| + | count[7..0] + delta[7..0] | Додавання |

| - | rightmost_x[] – leftmost_x[] | Віднімання |

Правила використання операторів додавання й віднімання:

§ Операндами даних операторів можуть бути групи (група змінних, група виводів модуля) і числа.

§ Якщо обидва операнди — групи, то вони повинні мати однакове число розрядів, що збігається із числом розрядів результату.

§ Якщо обидва операнди — числа, то автоматично здійснюється вирівнювання числа розрядів їхніх двійкових подань шляхом збільшення числа розрядів у двійковому поданні меншого операнда.

§ Якщо один операнд — число, а інший — група, то число перетвориться у двійкове число (групу двійкових розрядів). Якщо число розрядів у цій групі менше числа розрядів в іншому операнді, то вона автоматично розширюється. Якщо ж більше, то процесор повідомлень (Message Processor) пакета MAX+plus II видає повідомлення про помилку.

1.7.3. Оператори порівняння

У табл. 8 перераховані оператори порівняння, які можуть бути використані в логічних виразах.

Таблиця 8.

| Оператор порівняння | Приклад | Опис |

| = = (логічне) | addr[19..4] = = H”B800” | Дорівнює |

| != (логічне) | b1 != b3 | Нерівно |

| < (арифметичне) | fame[] < power | Менше |

| <= (арифметичне) | money[] <= power[] | Менше або дорівнює |

| > (арифметичне) | love[] > money[] | Більше |

| >= (арифметичне) | delta >= 0 | Більше або дорівнює |

Результат операції порівняння:

§ логічний нуль (GND), якщо умови порівняння не виконані;

§ логічна одиниця (VCC), якщо умови порівняння виконані.

Виділяються два типи операторів порівняння:

§ оператори логічного порівняння (Logical comparator);

§ оператори арифметичного порівняння (Arithmetic comparator).

Операндами оператора логічного порівняння можуть бути:

§ однорозрядні змінні й виводи модуля;

§ групи змінних і групи виводів модуля;

§ числа (у двійкових числах не повинен використовуватися символ "х" - символ невизначеного значення розряду).

При логічному порівнянні здійснюється побітове порівняння операндів, тому вони повинні мати однакове число розрядів. Якщо один операнд число, а інший - група, то число перетвориться у двійкове число (групу двійкових розрядів). Якщо число розрядів у цій групі менше числа розрядів в іншому операнді, то вона автоматично розширюється. Якщо ж більше, то процесор повідомлень (Message Processor) пакета MAX+plus II видає повідомлення про помилку.

Оператори арифметичного порівняння дозволяють порівнювати групи (змінних і виводів модуля) і числа.

При арифметичному порівнянні група інтерпретується як додатне двійкове число без знака, число розрядів в якого відповідає числу розрядів у групі. Тому операнди повинні мати однакове число розрядів. Якщо один операнд число, а іншої - група, то число перетвориться у двійкове число (групу двійкових розрядів). Якщо число розрядів у цій групі менше числа розрядів в іншому операнді, то вона автоматично розширюється. Якщо ж більше, то процесор повідомлень (Message Processor) пакета MAX+plus II видає повідомлення про помилку.

1.8. Пріоритет виконання операцій

У таблиці 9 зазначений пріоритет виконання (порядок виконання) операцій, використовуваних у логічних виразах.

Таблиця 9. Пріоритет виконання операцій

| Пріоритет виконання | Оператор | Опис |

| - | мінус | |

| ! | НІ | |

| + | Додавання | |

| - | Віднімання | |

| = = | Рівність | |

| != | Нерівність | |

| < | Менше | |

| <= | Менше або дорівнює | |

| > | Більше | |

| >= | Більше або дорівнює | |

| & | І | |

| !& | І-НІ | |

| $ | Виключаюче АБО | |

| !$ | Виключаюче АБО-НІ | |

| # | АБО | |

| !# | НІ |

Примітка: Чим менше число, що позначає пріоритет, тим вище пріоритет операнда.

1.9. Примітиви

Примітив - вбудований в пакет MAX+plus II і мову AHDL функціональний опис того або іншого внутрішнього ресурсу НВІС ПЛ фірми ALTERA .

У мові AHDL визначено два типи примітивів:

§ примітиви буферів;

§ примітиви тригерів: синхронних тригерів (Flipflop) і тригера засувки (Latch).

1.9.1. Примітиви буферів

У мові AHDL використовуються наступні примітиви буферів:

§ CARRY — буфер ланцюгового переносу;

§ CASCADE — буфер каскадного нарощування логічної функції;

§ ЕХР — буфер логічного розширювача;

§ GLOBAL — буфер глобального ланцюга поширення керуючого сигналу;

§ LCELL — буфер розміщення логічного осередку (макроосередку), що не видаляється ;

§ OPNDRN — буфер виходу з відкритим колектором;

§ SOFT — буфер розміщення логічного осередку (макроосередку), що видаляється;

§ TRI — буфер виходу зі Z станом.

Буфер ланцюгового переносу (CARRY)

Буфер має один вхід (IN) і один вихід (OUT). Правила використання буфера ілюструються на рис. 1. Відмітимо, що: § вихідний сигнал буфера може надходити на вхід тільки одного логічного елемента;Буфер глобального ланцюга поширення управляючого

Сигналу (GLOBAL)

■ тактового сигналу (Global Clock); ■ сигналу скидання тригера (Global Clear); ■ сигналу установки тригера (Global Preset);Буфер виходу з Z станом (TRI)

Якщо на вході ОЕ присутня логічна одиниця, то сигнал на виході OUT повторює сигнал, що надходить на вхід IN. Якщо логічний нуль, то вихід буфера TRI… Правила використання буфера TRI: § Сигнал з виходу буфера TRI повинен подаватися тільки на один вивід: типу вхід/вихід (BIDIR) або вихід (OUTPUT)…Загальна структура

Текстовий файл проекту мовою AHDL повинен містити, як мінімум, два розділи: Subdesign і Logic.Всі інші розділи і оператори є необов’язковими. Основні компоненти структури перераховані нижче в тому порядку, в якому їх слід використовувати, а саме:

Title Statement.

Parameters Statement.

Include Statement.

Constant Statement.

Define Statement.

Function Prototype Statement.

Options Statement.

Assert Statement.

Subdesign Section.

Variable Section.

- Instance Declaration.

- Node Declaration.

- Register Declaration.

- State Machine Declaration.

- Machine Alias- Declaration.

- If Generate Statement.

Logic Section.

- Assert Statemert. - Boolean Equations. - Boolean Control Equations.Title Statement

Приклад: TITLE “Binary COUNTER” Заголовок Binary COUNTER з'явиться на початку файлу звіту (Report File (.rpt))Parameters Statement

Parameters Statement дозволяє оголосити параметри, що управляють реалізацією параметризованих модулів. Приклад: 1. PARAMETERSInclude Statement

Приклади: 1. INCLUDE "Low-level_project.inc"; 2. INCLUDE "constant";Constant Statement

Приклади: 1. CONSTANT UPPER_LIMIT=H"130"; 2. CONSTANT BAR=1+UPPER_LIMIT DIV3+L0G2(256);Define Statement

Приклад: PARAMETERS (WIDTH); DEFINE MAX (a,b)=(a>b)?a:b;Function Prototype Statement

Приклади: 1. FUNCTION lpm_add_sub (Cin, dataa[LPM_WIDTH-1..0], datab[LPM_WIDTH-1..0], add_sub) -- входи модуляOptions Statement

§ LSB - молодший розряд (Least Significant Bit). При цьому індекси в групах повинні вказуватися в спадній, зліва направо, послідовності; § MSB - старший розряд (Most Significant Bit). При цьому індекси в групах… § ANY. При цьому порядок перерахування індексів у групі може бути довільним.Assert Statement

Приклад: ASSERT (WIDTH>0) REPORT "Width (%) must be a positive integer" WIDTHSubdesign Section

Приклад: SUBDESIGN First_project ( А, В[4..0] : INPUT=VCC;Variable Section

Змінна - це символічне ім'я: - лінії зв'язку; - лінії зв'язку із трьома станами;Logic Section

Правила використання розділу: § Розділ починається із ключового слова BEGIN і закінчується ключовим словом… 1. У розділі можуть бути використані:Групи

Однотипні змінні або виводи можуть бути об'єднані в одновимірну, двовимірну або часову групу.

3.4.1. Одновимірні й часові групи

Нижче наведене текстовий опис, що ілюструє використання одновимірних і часових груп:

SUBDESIGN GROUP_1

(

А[3..0] : INPUT; -- одновимірна група із чотирма членами

В[4..1] : INPUT; -- одновимірна група із чотирма членами

c,d,e,f : INPUT; -- однорозрядні входи

ОUT[5..2] : OUTPUT; -- одновимірна група зі чотирма членами

)

BEGIN

OUT[]=(A[] # В[1..4]) & !(c,d,e,f);

END;

Комбінаційна схема, що відповідає модулю GROUP_1, наведена на рис. 9.

Рис. 9.

Групи А[] і В[] мають однакове число членів, тому можливе порозрядне застосування оператора #: А[] # В[1..4].

При посиланні на групу В[4..1] її індекси перераховані у зворотному порядку В[1..4]. Тому при компіляції проекту процесор повідомлень сформує наступне попередження:

"Warning: Line 9, File c:max_workboole_1group_1.tdf:

Group range B[1..4] differs from declaration B[4..1]"

Якщо в логічному рівнянні використовуються всі члени групи, причому в тім же порядку, у якому вони були задані, то для посилання на таку групу можна скористатися скороченою формою запису: A[] замість А[3. .0].

(c,d,f,g) - часова група із чотирма членами. Вираз !(c,d,f,g) задає порозрядне виконання інвертування.

У виразі (А[] # В[1..4]) & !(c,d,e,f) операндами оператора & є дві чотирирозрядні групи: A[3] # B[1], A[2] # B[2], A[1] # B[3], A[0] # B[4], і !c, !d, !e, !f. Тому можливо його порозрядне застосування.

Значення однієї групи може бути присвоєно іншій групі (тобто між ними можна поставити знак рівності) тільки в тому випадку, коли вони мають однакове число розрядів. Тому група OUT[] так само є чотирирозрядною.

3.4.2. Двовимірні групи

Текстовий опис, що ілюструє застосування двовимірних груп наведено нижче:

SUBDESIGN GROUP 2

(

A[2..1] : INPUT;

R[1..2][2..1] : OUTPUT;

)

BEGIN

R[][] = (A[1..2], A[]);

END;

Відзначимо, що групи ліворуч і праворуч від знака рівності (=) мають однакове число розрядів. На рис. 10 представлена схема, що відповідає модулю GR0UP_2.

Рис. 10.

3.5. Таблиця істинності

Таблиця істинності логічної функції задається в такий спосіб

TABLE

_ _node_name, __node_name => __node_name, __node_name;

_ _input_value, __ input_value => __output_ value __output_ value;

_ input_value, input_value => __output_ value __output_ value;

_ input_value, input_value => __output_ value __output_ value;

END TABLE;

Відкриває таблицю ключове слово TABLE, а закривають ключові слова END TABLE, за яких слідує крапка з комою (;).

Перший після слова TABLE рядок визначає форму таблиці. У ньому, через кому, перераховуються аргументи (внутрішні змінні, входи або виходи модуля) та імена формованих логічних функцій (внутрішні змінні або виходи модуля). Аргументи й функції розділяє символ стрільця (=>). Наприкінці рядка ставиться крапка з комою.

У наступних рядках відповідно до заданої форми, вказуються набори аргументів і значення логічних функцій.

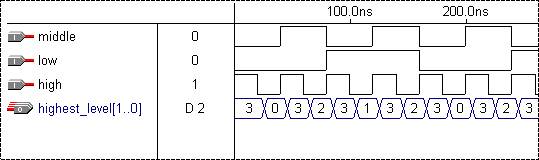

Розглянемо використання таблиці істинності на прикладі опису пріоритетного шифратора.

SUBDESIGN TRUTH_TABLE

(

high, middle, low :INPUT;

highest_level[1..0] :OUTPUT;

)

BEGIN

TABLE

high, middle, low => highest_level[];

1,x,x=>3;

0,1,x=>2;

0,0,1=>1;

0,0,0=>0;

END TABLE;

END;

Наведена таблиця істинності задає дві логічні функції від трьох аргументів. Якщо аргумент high=1, то при будь-яких значеннях аргументів middle і low (дані аргументи задані в таблиці символом "х" - don't care) групі виходів highest_level буде присвоєне значення В"11" і так далі. При рівності всіх аргументів логічному нулю групі виходів highest_level[] буде присвоєне значення В"00".

Примітка:У наведеному тексті програми функція двох змінних highest_level[] задана її десятковим еквівалентом (3 = В”11”, і так далі), що ілюструє можливість використання при описі алгоритму різних форм задання числа.

Оператор IF THEN

Оператор IF THEN може використовуватися в одній з наступних форм:

| IF __expression THEN __statement; __statement; ELSIF __expression __statement; __statement; ELSE __statement; __statement; END IF; | IF __expression THEN __statement; __statement; ELSE __statement; __statement; END IF; | IF __expression THEN __statement; __statement; END IF; |

Даний оператор, у загальному випадку, дозволяє послідовно оцінити істинність декількох логічних виразів і відповідно до отриманих результатів виконати ті або інші дії.

Розглянемо використання оператора IF THEN на прикладі опису пріоритетного шифратора, заданого в модулі TRUTH_TABLE таблицею істинності.

SUBDESIGN IF_THEN

(

high, middle, low :INPUT;

highest_level[1..0] :OUTPUT;

)

BEGIN

IF high == 1

THEN

highest_level[]=3;

ELSIF middle == 1

THEN

highest_level[]=2;

ELSIF low == 1

THEN

highest_level[]=1;

ELSE

highest_level[]=0;

END IF;

END;

Відзначимо, що операторові IF THEN внутрішньо властива пріоритетність. Так, вхід high, який перевіряється першим, має вищий пріоритет: якщо high=1, то при будь-яких значеннях сигналів на входах middle і low (їхні значення навіть не перевіряються) групі виходів highest_level буде присвоєне двійкове число В" 11". Вхід middle має більше низький пріоритет, а вхід low - нижчий.

Складений оператор IF THEN - оператор, що включає вираз ELSIF, компілятор інтерпретує в такий спосіб:

| Вихідний текст IF high == 1 THEN highest_level[]=3; ELSIF middle == 1 THEN highest_level[]=2; ELSIF low == 1 THEN highest_level[]=1; ELSE highest_level[]=0; END IF; END; | Інтерпретація компілятора IF high THEN highest_level[]=3; END IF; IF !high & middle THEN highest_level[]=2; END IF; IF !high &!middle & low THEN highest_level[]=1; END IF; IF !high &!middle & !low THEN highest_level[]=0; END IF; |

Оператор CASE

Оператор CASE може використовуватися в одній з наступних форм:

| CASE __expression IS WHEN __constant_vaiue => __statement; __statement WHEN __constant_vaiue => __statement; __statement WHEN OTHERS => __statement; __statement END CASE; | CASE __expression IS WHEN __constant_vaiue => __statement; __statement WHEN __constant_vaiue => __statement; __statement END CASE; |

Оператор CASE дозволяє оцінити значення однорозрядної змінної (однорозрядного виводу), групи змінних (групи виводів) і по результатах оцінки вибрати той або інший оператор для виконання.

Використання оператора CASE проілюструємо на прикладі опису пріоритетного шифратора, представленого раніше в модулях TRUTH_TABLE і IF_THEN.

SUBDESIGN CASE_

(

high, middle, low : INPUT;

highest_level[1..0] : OUTPUT;

)

BEGIN

CASE (high, middle, low) IS

WHEN B"1XX" => highest_level[]=3;

WHEN B"01X" => highest_level[]=2;

WHEN B"001" => highest_level[]=1;

WHEN OTHERS => highest_level[]=0;

END CASE;

END;

В операторі CASE оцінюється значення часової групи (high, middle, low). Якщо її значення відповідає:

■ двійковому числу В"1хх", то виконується оператор, що присвоює групі виходів highest_level[] десяткове число 3;

■ двійковому числу В"01х", то групі виходів highest_level[] присвоюється десяткове число 2;

■ двійковому числу В"001", то групі виходів highest_level[] присвоюється десяткове число 1;

■ іншим (WHEN OTHERS), не зазначеним вище трирозрядним двійковим числам, то групі виходів highest_level[] буде присвоєне десяткове число 0.

Нагадаємо, що двійкове число В"1хх" відповідає набору чисел: В"100”, В"101", В" 110", В"111". Тому оператор WHEN OTHERS => highest_level[]= у даному прикладі еквівалентний операторові WHEN В"000" => highest_level[]=0.

Нижче (рис. 11) наведено часові діаграми, отримані при моделюванні з використанням пакета MAX+plus II роботи пріоритетного шифратора

Рис. 11.

3.8. Базові значення логічних функцій

Необхідність у заданні базових значень логічних функцій виникає тоді, коли вони визначені не на всіх наборах аргументів. Базові значення можуть бути задані:

■ неявно (за замовчуванням);

■ явно.

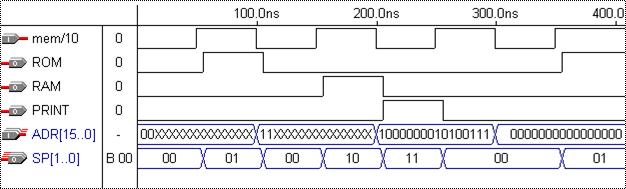

Базове значення, що задається за замовчуванням - логічний нуль. Проілюструємо неявне задання базових значень на прикладі:

SUBDESIGN DEFAULT_1

(

ADR[15..0], mem/io : INPUT;

ROM, RAM, PRINT, SP[1..0] : OUTPUT;

)

BEGIN

TABLE

mem/io, ADR[] => ROM, RAM, PRINT, SP[];

1, B"00xxxxxxxxxxxxxx" =>1, 0, 0, 1;

1, B"11xxxxxxxxxxxxxx" =>0, 1, 0, 2;

0, B"1000000010100111" =>0, 0, 1, 3;

END TABLE;

END;

Логічні функції ROM, RAM, PRINT, SP[2], SP[1] визначені не на всіх наборах аргументів. Оскільки немає явного задання їхніх базових значень, то за замовчуванням вони будуть дорівнювати нулю на всіх, не наведених в таблиці істинності наборах аргументів

Результати моделювання модуля DEFAULT_1 представлені на рис. 12

Рис. 12.

Для явного задання базових значень логічних функцій застосовується оператор DEFAULTS:

DEFAULTS ,

node_name = constant_value;

END DEFAULTS;

Використання цього оператора ілюструється в наступному прикладі:

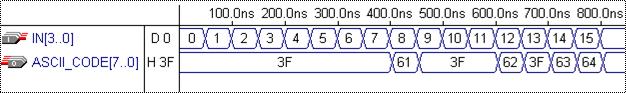

SUBDESIGN DEFAULT_2

(

IN[3..0] : INPUT;

ASCII_CODE[7..0] : OUTPUT;

)

BEGIN

DEFAULTS

ASCII_CODE[]=B"00111111"; -- величина коду, яка

-- задана за замовчуванням (код, що відповідає символу «?»)

END DEFAULTS;

TABLE

IN[] =>ASCII_CODE[];

8 => B"01100001"; -- ASCII код букви "а".

12 => B"01100010"; -- ASCII код букви "b".

14 => B"01100011"; -- ASCII код букви "c".

15 => B"01100100"; -- ASCII код букви "d".

END TABLE;

END;

Група виводів ASCII_CODE[] на всіх, не зазначених в таблиці істинності наборах аргументів, буде мати значення В"00111111", явно задане в операторі DEFAULTS.

При описі логічної функції за допомогою операторів CASE і IF THEN доцільно явне визначення її на всіх наборах аргументів.

SUBDESIGN DEFAULT_3

(

IN[3..0] : INPUT;

ASCII_CODE[7..0] : OUTPUT;

)

BEGIN

CASE IN[] IS

WHEN 8 => ASCII_CODE[]=B"01100001";-- ASCII код букви "а".

WHEN 12 => ASCII_CODE[]=B"01100010";-- ASCII код букви "b".

WHEN 14 => ASCII_CODE[]=B"01100011";-- ASCII код букви "c".

WHEN 15 => ASCII_CODE[]=B"01100100";-- ASCII код букви "d".

WHEN OTHERS => ASCII_CODE[]=B"00111111";-- ASCII код символу "?"

END CASE;

END;

У наведеному прикладі використана конструкція WHEN OTHERS (коли інші) оператора CASE. Ця конструкція задає групі виходів ASCII_CODE[] значення В"00111111" на всіх, не зазначених раніше в операторі CASE, наборах аргументів.

Результати моделювання логічно еквівалентних модулів DEFAULT_2 і DEFAULT_3 наведені на рис. 13

Рис.13.

Відмітимо, що якщо значення логічної функції на деяких набоpax аргументів для нас байдуже, то на цих наборах аргументів їй варто присвоїти значення В"х", що дозволить компіляторові більш ефективно мінімізувати логічну функцію.

Константи

■ зробити текстовий опис більше наочним; ■ спростити внесення змін, пов'язаних зі зміною фіксованих числових… Нижче представлений опис адресного декодера, у якому базові значення адрес задаються константами.Оператор FOR GENERATE

Оператор FOR GENERATE (оператор циклу) дозволяє спростити запис послідовності подібних логічних рівнянь і операторів, мови AHDL.

Оператор циклу має вигляд:

FOR __index_variable IN __range GENERATE

_ __statement;

_ __statement;

END GENERATE;.

Оператор задається в такий спосіб:

■ За ключовим словом FOR вказується символічне ім'я внутрішньої змінної оператора. Це ім'я не може збігатися з ім'ям констант, параметрів або змінних, використовуваних у текстовому описі.

■ Ключові слова IN ... ТО ... визначають границі зміни значень внутрішньої змінної оператора.

■ Границі задаються арифметичними виразами.

■ За ключовим словом GENERATE слідують логічні рівняння й оператори мови AHDL.

■ Оператор кінчається ключовими словами END GENERATE, за яким слідує крапка з комою (;).

Проілюструємо використання оператора FOR GENERATE для опису на вентильному рівні N-розрядного суматора, що має вхід і вихід переносу.

CONSTANT NUM_OF_ADDERS=8;

SUBDESIGN FOR_GEN

(

a[NUM_OF_ADDERS..1], b[NUM_OF_ADDERS..1], cin : INPUT;

c[NUM_OF_ADDERS..1], cout : OUTPUT;

)

VARIABLE

carry_out [(NUM_OF_ADDERS+1)..1] : NODE;

BEGIN

carry_out[1]=cin;

FOR i IN 1 TO NUM_OF_ADDERS GENERATE

c[i]=(a[i] $ b[i]) $ carry_out[i];

carry_out[i+1] = a[i] & b[i] # carry_out[i] & (a[i] $ b[i]);

END GENERATE;

cout = carry_out[NUM_OF_ADDERS+1];

END;

Опис, заданий оператором FOR GENERATE при NUM_OF_ADDERS = 4 відповідає наступним рівнянням:

c[1] = a[1] $ b[1] $ carry_out[1];

carry_out[2] = a[1] & b[1] # carry_out[1] & (a[1] $ b[1]);

с[2] = a[2] $ b[2] $ carry_out[2];

carry _out[3] = a[2] & b[2] # carry_out[2] & (a[2] $ b[2]);

с[3] = a[3] $ b[3] $ carry_out[3];

carry _out[4] = a[3] & b[3] # carry_out[3] & (a[3] $ b[3]);

c[4] = a[4] $ b[4] $ carry_out[4];

carry_out[5] = a[4] & b[4] # carry_out[4] & (a[4] $ b[4]);

Результати моделювання описаного суматора при NUM_0F_ADDERS=8 наведені на рис. 15

Рис. 15.

Відмітимо, що для зміни розрядності суматора досить у текстовому описі змінити значення константи NUM_OF_ADDERS.

Параметри

Значення параметра, на відміну від значення константи, може бути задане поза тим текстовим описом, у якому цей параметр визначений і… Нижче наведено поведінковий (алгоритмічний) опис суматора, розрядність якого…Оператор IF GENERATE

Оператор IF GENERATE дозволяє оцінити значення арифметичного виразу і за результатами оцінки сформувати той або інший опис проектованого модуля.

Оператор може використовуватися в повній або спрощеній формі.

Повна форма: Спрощена форма:

IF __expression GENERATE IF _expression GENERATE

__statement; __statement;

__statement; __statement;

ELSE GENERATE END GENERATE;

__statement;

__statement;

END GENERATE;

Оператор задається в такий спосіб:

■ За ключовим словом IF вказується оцінюваний арифметичний вираз.

■ За ключовим словом GENERATE слідують оператори мови AHDL, які будуть використані в текстовому описі при істинності оцінюваного арифметичного виразу.

■ При наявності ключових слів ELSE GENERATE за ними вказуються оператори, які будуть використані в текстовому описі в тому випадку, якщо оцінюваний арифметичний вираз хибний.

■ Оператор закінчується ключовими словами END GENERATE, за якими слідує крапка з комою (;).

Застосування оператора проілюструємо на прикладі текстового опису, що залежно від значення параметра Module_Type буде задавати або суматор, або віднімальщик розрядністю WIDTH.

PARAMETERS

(

WIDTH = 8,

MODULE_TYPE = "ADD"

);

SUBDESIGN IF_GEN

(

A[WIDTH..1], B[WIDTH..1] : INPUT;

RESULT[WIDTH..1], Cout : OUTPUT;

)

BEGIN

IF Module_Type == "ADD" GENERATE

(Cout,Result[]) = (GND,A[]) + (GND,B[]);

ELSE GENERATE

(Cout,Result[]) = (GND,A[]) - (GND,B[]);

END GENERATE;

END;

При вихідних значеннях параметрів компілятор синтезує восьмирозрядний суматор, результати моделювання якого наведені на рис. 16

Рис. 16.

Якщо поза текстовим описом (наприклад, командою Global Project Parameters меню Assign) параметру Module_Type присвоїти відмінне від ADD значення, то компілятор синтезує віднімальщик, результати моделювання якого наведені на рис. 17.

Рис. 17.

Нагадаємо, що підстановка значень параметрів і формування відповідного текстового опису здійснюється компілятором на етапі перевірки синтаксису. Тому застосування оператора IF GENERATE не приводить до використання додаткових логічних ресурсів НВІС ПЛ.

Оператор ASSERT

Оператор ASSERT дозволяє контролювати істинність арифметичного виразу, операндами якого є: параметри, числа, позначені арифметичні вирази, а також значення вбудованої в пакет функції USED.

Функція USED застосовується для перевірки виводів модуля. Аргументом функції є ім'я виводу модуля. Значення, що повертається:

■ FALSE - якщо даний вивід модуля не підключений при використанні модуля як компонента в описі більш високого рівня ієрархії;

■ TRUE - якщо вивід підключений.

Як ілюстрацію розглянемо наведений нижче текстовий опис, що базується на представленому раніше описі модуля IF_GEN.

PARAMETERS

(

WIDTH = 8,

MODULE_TYPE = "ADD"

);

ASSERT (WIDTH > 0)

REPORT "WIDTH of % must be more then %" Module_Type, WIDTH

SEVERITY ERROR;

SUBDESIGN ASSERT_

(

A[WIDTH..1],B[WIDTH..1] : INPUT;

RESULT[WIDTH..1], Cout : OUTPUT;

)

BEGIN

ASSERT (Module_Type =="ADD") or (Module_Type =="SUB")

REPORT "Module_Type must be ""ADD"" or ""SUB"" but not %" Module_Type

SEVERITY ERROR;

IF Module_Type == "ADD" GENERATE

(Cout,Result[]) = (GND,A[]) + (GND,B[]);

ELSE GENERATE

(Cout,Result[]) = (GND,A[]) - (GND,B[]);

END GENERATE;

END;

У наведеному прикладі оператор ASSERT використовується для контролю значення параметрів WIDTH і Module_Type.

Так, якщо значення параметра Module_Type, задане поза даним текстовим описом, відмінно від ADD і SUB (наприклад, дорівнює MIN), то компілятор сформує наступне повідомлення:

Error: Line 17, File c:max_workassert_.tdf:

Module_Type must be "ADD" or "SUB" but not MIN

Оскільки «рівень строгості» даного повідомлення - ERROR, то компілятор припинить роботу.

Відзначимо, що при «рівнях строгості» WARRING і INFO компілятор продовжує роботу.

3.14. Примітиви

Для використання в текстовому описі модуля примітива необхідно звернутися до вбудованого в пакет функціонального опису даного примітива й зіставити його виводам: числа, константи, змінні або виводи модуля.

У мові AHDL визначені два способи звертання до примітива:

■ безпосереднє звертання (In_line Reference);

■ присвоєння примітиву символічного імені, тобто оголошення його змінною або звертання до нього як до змінної.

Безпосереднє звертання до примітива здійснюється в такий спосіб:

■ вказується вихід (або внутрішня змінна) модуля, на який передається сигнал з виходу примітива;

■ далі ставиться знак рівності й ім'я примітива;

■ за ім'ям примітива в круглих дужках, через кому перераховуються передані значення:

- числа,

- константи,

- змінні або виводи модуля, що зіставляються входам примітива;

■ за круглими дужками ставиться крапка з комою.

Зіставлення входів примітива з переданими значеннями може здійснюватися:

■ позиційно;

■ за іменами.

При позиційному зіставленні порядок перерахування переданих значень повинен відповідати порядку перерахування входів, використаному в описі прототипу примітива.

Вихід модуля (внутрішня змінна)=

Ім'я примітива (передане значення, передане значення,...);

Як приклад розглянемо текстовий опис схеми, представленої на рис.18

Рис. 18

Текстовий опис:

SUBDESIGN Prim_in_line1

(

D_in, Enadle : INPUT;

D_tri : OUTPUT;

)

BEGIN

D_tri = TRI(D_in, Enable);

END;

При описі присвоєння в програмі можливі наступні варіанти, що ілюструють метод присвоєння за іменами.

D_tri = TRI(.IN = D_in, OE = Enable);

D_tri = TRI(OE = Enable,.IN = D_in);

Відзначимо, що прототипи примітивів вбудовані в пакет, і для їхнього підключення до текстового опису, оператор INCLUDE не використовується. Прототип примітива TRI у пакеті MAX+plus II заданий у такий спосіб:

FUNCTION TRI (IN, OE)

RETURNS (OUT);

При звертанні до примітива в списку переданих значень першим зазначений вхід D_in. Тому він буде з'єднаний із входом, зазначеним першим в описі прототипу примітива. Відповідно, вхід Enable модуля буде з'єднаний із входом ОЕ примітива TRI.

Якщо деякі із входів примітива не використовуються, то відповідні позиції в списку переданих значень повинні бути залишені порожніми. Проілюструємо це на прикладі текстового опису схеми, наведеної на рис.19.

Рис. 19.

Текстовий опис:

SUBDESIGN Prim_in_line2

(

D_in, CLK, Enadle : INPUT;

D_out : OUTPUT;

)

BEGIN

D_out = DFFE(D_in, CLK, , ,Enable);

END;

У даному прикладі використаний примітив DFFE, прототип якого в пакеті MAX+plus II має вигляд:

FUNCTION DFFE (D, CLK, CLRn, PRn, ENA)

RETURNS (Q);

Входи CLRn і PRn примітива в модулі Prim_in_line2 не використовуються, тому їхні позиції виділені в списку переданих значень комами й залишені порожніми.

При зіставленні переданих значень і входів примітива за іменами у списку значень, що передаються, через кому перераховуються: вхід і значення, що передається.

Формат запису:

Вихід модуля (внутрішня змінна) = Ім'я примітива

(ім'я виходу=передане значення, ім'я виходу = передане значення,...);

Пари можуть бути розташовані в довільному порядку, тобто незалежно від того, у якій послідовності перераховані входи в описі прототипу примітива. Невикористані входи примітива в списку переданих значень не вказуються.

Наведений нижче текстовий опис схеми, логічно еквівалентний текстовому опису модуля Prim_in_line2, ілюструє даний спосіб зіставлення.

SUBDESIGN Prim_in_line3

(

D_in, CLK, Enadle : INPUT;

D_out : OUTPUT;

)

BEGIN

D_out = DFFE(.CLK = CLK, .D = D_in, .ENA = Enable);

END;

Інший спосіб звертання до примітива — звертання до нього як до змінної.

При реалізації цього способу, примітив, насамперед, варто оголосити змінною. Для цього в розділі змінних (Variable Section) символічному імені або групі символічних імен зіставляється примітив. Оголошена в такий спосіб змінна, а так само кожна змінна з оголошеної групи змінних, буде мати той же набір виводів, що й примітив.

Звертання до конкретного виводу примітива здійснюється шляхом вказівки імені змінної, розділяючої крапки й імені виводу примітива.

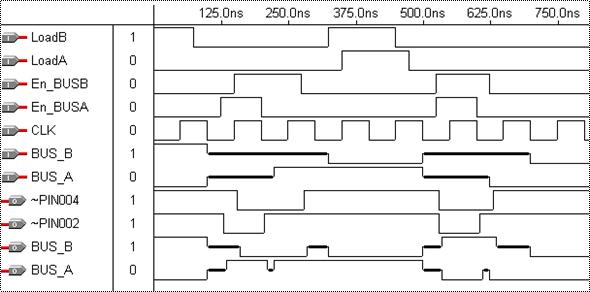

Як приклад, що ілюструє такий спосіб звертання до примітива, розглянемо текстовий опис схеми, наведеної на рис. 20.

Текстовий опис:

SUBDESIGN PRIM_VAR

(

En_BUSA,En_BUSB,Load,Load,CLK : INPUT;

BUS_A, BUS_B : BIDIR;

)

VARIABLE

RG_BUSA, RG_BUSB : DFFE;

BUF_A, BUF_B : TRI;

BEGIN

(RG_BUSA, RG_BUSB).CLK = CLK;

RG_BUSA.(D, ENA) = (BUS_B, Load);

RG_BUSB.(D, ENA) = (BUS_A, Load);

BUF_A.(IN, OE) = (RG_BUSA.Q,En_BUSA);

BUF_B.(IN, OE) = (RG_BUSB.Q,En_BUSB);

BUS_A = BUF_A.OUT;

BUS_B = BUF_B.OUT;

END;

Рис.2.20.

У даному прикладі оголошені чотири змінні. Змінні RG_BUSA і RG_BUSB позначають примітиви тригерів DFFE, а змінні BUF_A і BUF_B - примітиви буферів з Z станом.

Перше логічне рівняння текстового опису задає з'єднання входу CLK модуля із входами CLK двох тригерів. Четверте логічне рівняння визначає зв'язок виходу Q одного із тригерів (тригера, позначеного RG_BUSA) і входу En_BUSA модуля із входами IN і ОЕ буферa TRI (буфера, позначеного BUF_A). Шосте логічне рівняння описує підключення виходу буфера TRI (буфера, позначеного BUF_A) до виводу BUS_A модуля.

Результати моделювання створеного модуля наведені на рис. 21.

Рис. 21.