Сигналу (GLOBAL)

Буфер GLOBAL дозволяє явно вказати компіляторові на необхідність використання глобального, який проходить через всю НВІС, неперервного ланцюга для поширення:

■ тактового сигналу (Global Clock);

■ сигналу скидання тригера (Global Clear);

■ сигналу установки тригера (Global Preset);

■ сигналу дозволу виходу (Global Output Enable).

Буфер має один вхід (IN) і один вихід (OUT). Використання буфера ілюструються на рис. 3.

Відмітимо, що:

■ на вхід буфера GLOBAL повинен надходити сигнал зі спеціалізованого входу НВІС (Dedicated Input). При цьому між 6уфером і спеціалізованим входом може стояти інвертор. У НВІС сімейств FLEX 6000 і FLEX10K на вхід буфера можна подавати сигнали, породжувані на внутрішніх логічних ресурсах НВІС;

■ сигнал з виходу буфера (або його інверсію) варто подавати на:

■ входи асинхронної установки (PRn) і скидання (CLRn) тригера;

- вхід синхронізації тригера (CLK),

- вхід дозволу виходу (Output Enable) буфера TRI.

Рис. 3.

Якщо буфер GLOBAL використовується неправильно, то компілятор пакета ігнорує його, а процесор повідомлень (Message Processor) видає попередження.

Альтернативою використанню буфера GLOBAL є установка опцій Automatic Global (меню Assign > Global Project Logic Synthesis]

1.9.6. Буфер розміщення логічного осередку (LCELL),

що не видаляється

Буфер LCELL дозволяє явно вказати компіляторові на необхідність використання логічного елемента (макроосередку). Даний буфер не може бути вилучений компілятором.

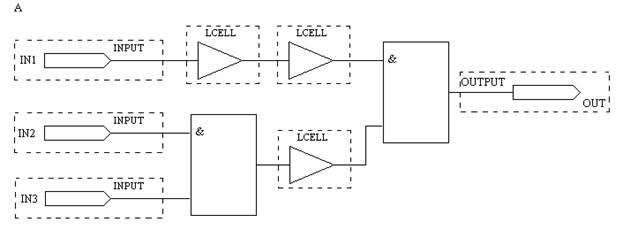

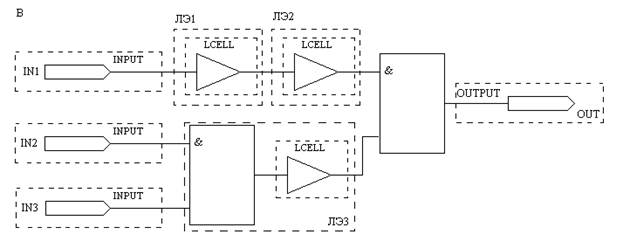

Буфер має один вхід (IN) і один вихід (OUT). На рис. 4 ілюструються особливості використання буфера LCELL.

Схема, представлена на рис. 4А, буде реалізована на чотирьох логічних елементах (макроосередках) (рис. 4В). Якщо ж зі схеми на рис. 4А забрати всі буфери LCELL, то для її реалізації буде потрібно всього один логічний елемент (макроосередок) (рис. 4С).

На рис. 5 показано, як за допомогою буфера LCELL може бути створена комбінаційна схема зі зворотним зв'язком.

Рис. 4.А.

Рис. 4.В.

Рис. 4.С.

Рис. 5.

Буфер LCELL не слід застосовувати для затримки сигналу, тому що в цьому випадку затримка поширення сигналу буде залежати від навколишньої температури, напруги живлення, технології виготовлення НВІС і, отже, не буде стабільною.

Пакет MAX+plus II дозволяє встановити режим автоматичного включення буферів LCELL як на етапі синтезу комбінаційної схеми модуля, так і її розміщення в НВІС. Це в деяких випадках дозволяє зменшити апаратні витрати (шляхом виділення загальних термів у синтезованих компілятором логічних рівняннях і їхній багаторівневій реалізації), а також забезпечити компіляторові додаткові можливості при розміщенні синтезованих схем у НВІС програмувальної логіки.

1.9.7. Буфер виходу з відкритим колектором (OPNDRN)

Буфер OPNDRN дозволяє явно вказати компіляторові на необхідність використання виходу з відкритим колектором.

Буфер має один вхід (IN) і один вихід (OUT).

Якщо на вхід буфера OPNDRN надходить логічний нуль, то на виході також буде логічний нуль. Якщо ж вхідний сигнал - логічна одиниця, то вихід буфера буде в Z стані.

Буфер OPNDRN еквівалентний буферу TRI, у якого на вхід IN надходить логічний нуль, а на вхід ОЕ - довільний сигнал.

Правила використання буфера OPNDRN:

§ Сигнал з виходу буфера повинен подаватися тільки на один вивід типу вхід/вихід (BIDIR).

§ Якщо сигнал з виходу буфера надходить на логічні елементи НВІС, то його необхідно подати й на вивід типу вхід/вихід (BIDIR).

Буфер OPNDRN може використовуватися тільки в НВІС сімейств MАХ 7000S і FLEX10K, для інших сімейств він автоматично перетвориться в буфер TRI.

При реалізації пристрою на НВІС сімейств MAX7000S або "FLEX10K і включеної опції Automatic Open-Drain (меню Assign > Global Project Logic Synthesis) компілятор перетворить буфер OPNDRN в:

§ буфер TRI, на вхід IN якого подається постійний логічний нуль (GND), а на вхід ОЕ - довільний сигнал;

§ буфер TRI, на вхід IN якого подається інверсне значення сигналу, що подається на вхід ОЕ.

1.9.8. Буфер розміщення логічного осередку (SOFT),

що видаляється

Буфер SOFT дозволяє вказати компіляторові на можливість використання логічного елемента (макроосередку). Буфер має один вхід (IN) і один вихід (OUT).

У процесі синтезу проекту компілятор перевіряє чи дозволить використання логічного елемента (макроосередку) замість буфера SOFT:

§ зменшити апаратні витрати (за рахунок виділення загальних термів багаторівневої реалізації логічної функції);

§ забезпечити додаткові можливості при розміщенні проекту в НВІС.

Якщо ні, то буфер SOFT видаляється із синтезованої схеми, якщо так, заміняється буфером LCELL.