рефераты конспекты курсовые дипломные лекции шпоры

- Раздел Изобретательство

- /

- Моделирование элементов второго иерархического уровня

Реферат Курсовая Конспект

Моделирование элементов второго иерархического уровня

Моделирование элементов второго иерархического уровня - раздел Изобретательство, АВТОМАТИЗИРОВАННОЕ ПРОЕКТИРОВАНИЕ СЛОЖНЫХ СИСТЕМ В КОМПЬЮТЕРНОЙ СИСТЕМОТЕХНИКЕ Цель Работы: Разработка Функциональной Схемы Устройства. Полу...

Цель работы:

Разработка функциональной схемы устройства. Получение и закрепление практических навыков проектирования и моделирования елементов второго иерархического уровня в системе автоматизированного проектирования OrCAD

Теоретические сведения:

Элементами 2 иерархического уровня для данного примера являются:

Триггеры RS, D;

Сумматоры;

Мультиплексоры;

Схемы реализуются на элементах первого иерархического уровня.

Триггер – простейшее последовательное логическое устройство, которое может находиться в одном из двух возможных состояний и переходить из одного состояния в другое под воздействием входных сигналов. Триггеры являются базовым элементом последовательностных логических устройств. Входы триггера разделяют на информационные и управляющие (вспомогательные). Это разделение в значительной степени условно. Информационные входы используются для управления состоянием триггера. Управляющие входы обычно используются для предварительной установки триггера в некоторое состояние и для синхронизации. Триггеры чаще всего имеют 2 выхода: прямой Q и инверсный Qi. Триггеры классифицируют по различным признакам:

· по способу приема информации;

· принципу построения;

· функциональным возможностям.

Различают асинхронные и синхронные триггеры.

Асинхронный триггер изменяем свое состояние непосредственно в момент появления соответствующего информационного сигнала.

Синхронные триггеры реагируют на информационные сигналы только при наличии сигнала на входе синхронизации.

Синхронные триггеры в свою очередь подразделяют на триггеры со статическим (статические) и динамическим (динамические) управлением по входу синхронизации С. Статические триггеры воспринимают информационные сигналы при подаче на вход С логической единицы (прямой вход) или логического нуля (инверсный вход). Динамические триггеры воспринимают информационные сигналы при изменении (перепаде) сигнала на входе С от "0" к "1" (прямой динамический С-вход) или от "1" к "0" (инверсный динамический С-вход).

Статические триггеры в свою очередь подразделяют на одноступенчатые (однотактные) и двухступенчатые (двухтактные). В одноступенчатом триггере имеется одна ступень запоминания информации, а в двухступенчатом — две такие ступени. Вначале информация записывается в первую ступень, а затем переписывается во вторую и появляется на выходе. Двухступенчатый триггер обозначают через "ТТ".

По функциональным возможностям триггеры разделяют на следующие классы:

• с раздельной установкой состояния "0" и "1" (RS-триггеры);

• универсальные (JK-триггеры);

• с приемом информации по одному входу D (D-триггеры, или триггеры задержки);

• со счетным входом Т (Т-триггеры).

Входы триггеров обычно обозначают следующим образом:

S —- вход для установки в состояние "1";

R — вход для установки в состояние "0";

J — вход для установки в состояние "1" в универсальном триггере;

К — вход для установки в состояние "0" в универсальном триггере;

Т — счетный (общий) вход;

D — вход для установки в состояние "1" или в состояние "0";

V — дополнительный управляющий вход для разрешения приема информации (иногда используют букву Е вместо V).

На базе триггеров и логических элементов могут быть построены более сложные устройства, необходимые для дальнейшего проектирования конечного аппарата. Например, регистры, сумматоры, счетчики, мультиплексоры и т.д.

Сумматоры. Полный сумматор – устройство, предназначенное для сложения трех одноразрядных двоичных чисел А, В и С. Такая задача возникает при поразрядном сложении двух одноразрядных чисел, когда в качестве третьего слагаемого приходится учитывать перенос из предыдущего (младшего) разряда. Построение функциональной схемы полного сумматора можно выполнить в соответствии с таблицей его функционирования (табл. 1). В реальных схемах полный сумматор выполняется из двух полусумматоров.

Полусумматоры. Полусумматор, в отличие от полного сумматора, обеспечивает выполнение операции суммирования двух одноразрядных двоичных чисел А и В без учета сигнала переноса из младшего разряда. В результате сложения в общем случае наряду с суммой может получиться перенос. Функционирование полусумматора описывает табл. 2.

Таблица 1

| № | Ai | Bi | Pi-1 | Si | Pi |

Таблица 2

| Ai | Bi | Si | Pi |

Мультиплексоры. Мультиплексором называется комбинационная схема, имеющая M+2M входов и один выход, где М – число адресных входов, а 2M – число информационных входов мультиплексора. Адреса представляют в двоичном коде, и им присваивается номер j. Каждому адресу с номером j соответствует свой информационный вход Аj, сигнал которого при данном адресе приходит на выход. Основным назначением мультиплексора является коммутация 2М входных сигналов на один выход. Мультиплексоры могут использоваться в качестве устройства для выбора соответствующего канала

Регистры. Регистрами называются устройства, выполняющие функции приема, хранения и передачи информации. Информация в регистре хранится в виде числа (слова), представленного комбинацией сигналов 0 и 1. Каждому разряду числа, записанному в регистр, соответствует свой разряд регистра, выполненный, как правило, на основе триггеров. Основным классификационным признаком, по которому различают регистры, является способ записи информации или кода числа в регистр. По этому признаку можно выделить регистры 3-х типов:

· Параллельные

· Последовательные

· Параллельно-последовательные

В параллельные регистры запись числа осуществляется параллельным кодом, т.е. во все разряды одновременно.

Последовательные регистры характеризуются последовательной записью кода числа, начиная с младшего или старшего разряда путем последовательного сдвига кода тактирующими импульсами.

Регистры параллельно-последовательного типа имеют входы как для параллельной, так и для последовательной записи кода числа.

Параллельные регистры (регистры памяти) используются для записи, хранения и считывания небольшого объема цифровой информации (одного или двух байтов). Для приема, хранения и считывания n бит информации регистр памяти должен состоять из n триггеров и дополнительных схем совпадения.

Сдвигающие (последовательные) регистры используются для сдвига n-разрядных чисел в одном направлении. Кроме того, их можно применить для сдвига нечисловой информации (при построении из них счетчиков).

Счетчики.Счетчиком называется устройство, осуществляющее счет числа входных импульсов и фиксирующее это число в каком-либо коде. Счетчики делятся на суммирующие, вычитающие и реверсивные. Суммирующий счетчик предназначен для выполнения счета в прямом направлении, т.е. для сложения. С приходом очередного импульса его содержимое увеличивается на 1. Вычитающий счетчик предназначен для выполнения счета в обратном направлении, т.е. в режиме вычитания. Каждый импульс, поступающий на вход такого счетчика, уменьшает его содержимое на 1. Реверсивными называют такие счетчики, которые могут работать в режиме сложения и в режиме вычитания. Счетчики могут быть построены на основе счетных триггеров, регистров и кольцевых схем.

Ход работы:

1. Согласно индивидуальному заданию спроектировать элементы 2-го уровня иерархии:

Элементы 2-го уровня иерархии:

Триггеры RS, D; JK, T;

Сумматоры;

Мультиплексоры;

на базе логики требуемой элементной базы;

2. Подать на информационные и управляющие входы все возможные разрешенные комбинации цифровых сигналов.

3. Получить временные диаграммы входных и выходных сигналов и оценить задержку каждого спроектированного триггера.

1. Пример моделирования D-триггера.

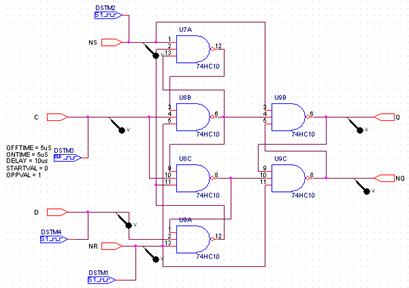

На рисунке представлена схема D-триггера.

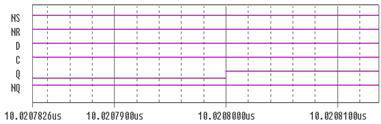

Результаты моделирования:

Определяем временные характеристики элемента:

По результатам моделирования видно, что синхроимпульс переключается в 10.0 ms, а на выходе триггера сигнал появляется в 10,0208 ms. Следовательно, время задержки при переключении из 0 в 1 равно 20,8 нс

Аналогичным образом определяем время задержки при переключении из "1" в "0":

Задержка при переключении из "1" в "0" равна 30,8 нс.

– Конец работы –

Эта тема принадлежит разделу:

АВТОМАТИЗИРОВАННОЕ ПРОЕКТИРОВАНИЕ СЛОЖНЫХ СИСТЕМ В КОМПЬЮТЕРНОЙ СИСТЕМОТЕХНИКЕ

В КОМПЬЮТЕРНОЙ СИСТЕМОТЕХНИКЕ... Учебное пособие... Часть...

Если Вам нужно дополнительный материал на эту тему, или Вы не нашли то, что искали, рекомендуем воспользоваться поиском по нашей базе работ: Моделирование элементов второго иерархического уровня

Что будем делать с полученным материалом:

Если этот материал оказался полезным ля Вас, Вы можете сохранить его на свою страничку в социальных сетях:

| Твитнуть |

Хотите получать на электронную почту самые свежие новости?

Новости и инфо для студентов