рефераты конспекты курсовые дипломные лекции шпоры

- Раздел Образование

- /

- Довідкові матеріали по елементам

Реферат Курсовая Конспект

Довідкові матеріали по елементам

Довідкові матеріали по елементам - раздел Образование, Нарошування розмірності пріоритетного шифратора 10 Кп1 Шостнадцятиканальний Інвертуючий Стробуємий Муль...

КП1

Шостнадцятиканальний інвертуючий стробуємий мультиплексор з адресним селектором (12-заг.24- +5В).

Таблиця істинності КП1

Таблиця 1

A8

A8

| A4 | A2 | A1 | _ E | Вихід |

| X | X | X | X | ||

| ___ DI0 | |||||

| ___ DI1 | |||||

| ___ DI2 | |||||

| ___ DI3 | |||||

| ___ DI4 | |||||

| ___ DI5 | |||||

| ___ DI6 | |||||

| ___ DI7 | |||||

| ___ DI8 | |||||

| ___ DI9 | |||||

| ___ DI10 | |||||

| ___ DI11 | |||||

| ___ DI12 | |||||

| ___ DI13 | |||||

| ___ DI14 | |||||

| ___ DI15 |

Рис.1.

КП5

Восьмиканальний інвертуючий мультиплексор з адресним селектором (7-заг.,14-+5В).

Див. таблицю КП1 з другої по дев’яту строку.

|

Рис.2.

КП15

Восьмиканальний мультиплексор з адресним селектором та третім станом виходу

(8-заг., 16-+5В).

Таблиця істинності КП15

Таблиця 2

| A4 | A2 | A1 | __ OE | D0 |

| X | X | X | Z | |

| DI0 | ||||

| DI1 | ||||

| DI2 | ||||

| DI3 | ||||

| DI4 | ||||

| DI5 | ||||

| DI6 | ||||

| DI7 |

Рис.3.

ИД5

Два дешифратора / демультиплексора з відкритим колекторним входом (8-заг., 16-+5В).

Відрізняється від ИД4 лише наявністю вихідних каскадів з відкритими колекторами.

Таблиця істинності ИД5

Таблиця 3

Таблиця 3

| DI2 | DI1 | _ E1 | E2 | ___ D000 | ___ D001 | ___ D002 | ___ D003 |

| X | X | X | |||||

| X | X | X |

Рис.4.

ИД19

Дешифратор / демультиплексор (4x16 - повний дешифратор) з відкритим колекторним входом.(12-заг.,24-+5В).Відрізняється від ИД3 лише наявністю вихідних каскадів з відкритими колекторами.

Таблиця істинності ИД19

Таблиця 4

Таблиця 4

| _ E1 | _ E2 | DI8 | DI4 | DI2 | DI1 | Вихід |

| X | X | X | X | На усіх виходах лог. ”1”. | ||

| X | X | X | X | |||

| X | X | X | X |

Рис.5.

ИД7

Дешифратор/демультиплексор (3x8) ,(8-заг.,16-+5В).У режимі демультиплексора адресний код подають на вхід DI,а один з входів Е використовується як інформаційний.

Таблиця істинності ИД7

Таблиця 5

| DI4 | DI2 | DI1 | _ E1 | _ E2 | E3 | Вихід |

| X | X | X | X | X | На усіх виходахлог . “1”. | |

| X | X | X | X | X | ||

| X | X | X | X | X |

|

Рис.6.

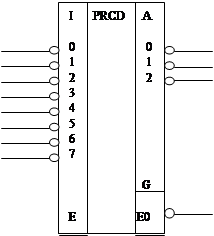

ИВ1

Восьмирічний шифратор пріоритетів. Вихідний сигнал G є сигналом присутності збуджених інформаційних розрядів. Сигнал Е0 є сигналом відсутності збуджених розрядів і при каскадуванні грає роль дозволяючего для суміжного каскаду.(8-заг.,16-+5В).

Таблиця істинності ИВ1

Таблиця 6

| _ Е | _ І7 | _ І6 | _ І5 | _ І4 | _ І3 | _ І2 | _ І1 | _ І0 | _ А2 | _ А1 | _ А0 | _ G | _ E0 |

| X | X | x | x | x | x | x | X | ||||||

| X | |||||||||||||

| X | X | ||||||||||||

| X | X | X | |||||||||||

| X | X | X | X | ||||||||||

| X | X | X | X | X | |||||||||

| X | X | X | X | X | X | ||||||||

| X | X | X | X | X | X | X |

|

Рис.7.

ИВ2

Восьмирічний шифратор пріоритетів з трьома станами виходу (8-заг.,16-+5В).ИВ2 відрізняється від ИВ1 лише наявністю високоімпедансного стану виходу, в котре він переходить у двох випадках при Е =1 і Е =0 .

| |||

| |||

| |||

Рис.8.

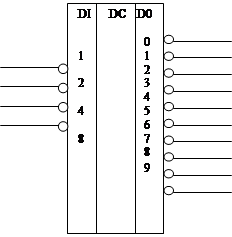

ИВ3

Двоічно - десятичний шифратор пріоритетів (8-заг.,16-+5В).

Таблиця істинності ИВ3

Таблиця 7

| _ I8 | _ І7 | _ І6 | _ І5 | _ І4 | _ І3 | _ І2 | _ І1 | _ І0 | _ А3 | _ А2 | _ А1 | _ A0 |

| X | ||||||||||||

| X | X | |||||||||||

| X | X | X | ||||||||||

| X | X | X | X | |||||||||

| X | X | X | X | X | ||||||||

| X | X | X | X | X | X | |||||||

| X | X | X | X | X | X | X | ||||||

| X | X | X | X | X | X | X | X |

|

Рис.9.

ИД6

Двоічно-десятичний дешифратор (4x10) перетворювач двоічно-десятичного коду в десятичний (8-заг.,16-+5В).

Таблиця істинності ИД6

Таблиця 8

DI8 DI8

| DI4 | DI2 | DI1 | Вихід |

Рис.10.

ИД10

Двоічно-десятичний дешифратор (4x10) перетворювач двоічно-десятичного коду в десятичний й з відкритим колекторним виходом (8-заг.,16-+5В).

Таблиця істинності ИД10

Таблиця 9

Таблиця 9

| DI8 | DI4 | DI2 | DI1 | Вихід |

Рис.11.

ИД12

Дешифратор (3x8) з відкритим емітерним виходом.

Таблиця істинності ИД12

Таблиця 10

| _ E | DI4 | DI2 | DI1 | Виходи | |||||||

| X | X | X |

|

| ||||||

| ||||||

| ||||||

| ||||||

| ||||||

|

Рис.12.

[Ћ1]

– Конец работы –

Эта тема принадлежит разделу:

Нарошування розмірності пріоритетного шифратора 10

C... Вступ Короткі теоретичні положення Дешифратори...

Если Вам нужно дополнительный материал на эту тему, или Вы не нашли то, что искали, рекомендуем воспользоваться поиском по нашей базе работ: Довідкові матеріали по елементам

Что будем делать с полученным материалом:

Если этот материал оказался полезным ля Вас, Вы можете сохранить его на свою страничку в социальных сетях:

| Твитнуть |

Хотите получать на электронную почту самые свежие новости?

Новости и инфо для студентов