ОТЧЕТ ПО УЧЕБНОЙ ПРАКТИКЕ Пояснительная записка

Министерство образования Иркутской области

ОП 230113.13.01.23 ПЗ ОГБОУСПО «ИАТ»

ОТЧЕТ ПО УЧЕБНОЙ ПРАКТИКЕ

Пояснительная записка

Зав.отделением Руководитель

Л. В. Петкевич Л. К. Роднина

Дата___________ Дата___________

Подпись________ Подпись________

Зав. циклом Студент

Л. К. Роднина Р. И. Скулин

Дата___________ Дата___________

Подпись________ Подпись________

2013

2013

Содержание

Введение.....................................................................................................

Введение.....................................................................................................

1. Справочные сведения по электронным компонентам (задание 1).......

2. Генераторы и схемы задержки (задание 2)..........................................

3. Восьмиразрядное АЛУ (задание 3)......................................................

4. Проектирование цифровых устройств в системе Quartus II

(задание 4)..............................................................................................

5. Проектирование цифровых устройств в системе Quartus II.

Бегущий огонь (задание 5)....................................................................

6. Проектирование цифровых устройств в системе Quartus II.

Генератор псевдослучайных последовательностей (задание 6)..........

Заключение.................................................................................................

Список используемой литературы............................................................

Введение

Профессиональная САПР Quartus II предназначена для проектирования ЦУ с высокой степенью интеграции, включая разработку законченных систем на одном программируемом кристалле ПЛИС (SOPC – System-on-a-programmable-chip).

При работе с микросхемами программируемой логики фирмы Altera основным инструментом проектирования ЦУ является САПР Quartus II. Данная САПР поддерживает все этапы проектирования: создание проекта, компиляция, верификация (моделирование) и программирование ПЛИС.

VHDL (англ. VHSIC (Very high speed integrated circuits) Hardware Description Language) – язык описания аппаратуры интегральных схем. Язык проектирования VHDL является базовым языком при разработке аппаратуры современных вычислительных систем.

VHDL создан как средство описания цифровых систем, однако существует подмножество языка – VHDL AMS (Analog Mixed Signal), позволяющее описывать как чисто аналоговые, так и смешанные, цифро-аналоговые схемы.

1 Результат выполнения задания №1«Справочные сведения

Результат выполнения задания №1«Справочные сведения

по электронным компонентам»

Микросхема К155ЛА1

Микросхема К155ЛА1 представляет собой два логических элемента 4И-НЕ.

На рисунке 1.1 представлено УГО триггера К155ЛА1.

На рисунке 1.1 представлено УГО триггера К155ЛА1.

Рисунок 1.1 –УГО К155ЛА1

Корпус микросхемы К155ЛА1 типа 201.14-1, масса около 1.

В таблице 1.1 приведена таблица истинности для рассматриваемого элемента.

Таблица 1.1

Таблица истинности

| Состояние микросхемы К155ЛА1(7420) | ||||

| Вход | Выход | |||

| 1 (9) | 2 (10) | 4 (12) | 5 (13) | 6 (8) |

| В | В | В | В | Н |

| Н | х | х | х | В |

| х | Н | х | х | В |

| х | х | Н | х | В |

| х | х | х | Н | В |

В таблице 1.2 приведены электрические параметры

Таблица 1.2 – Электрические параметры

| Номинальное напряжение питания | 5В + 5% | |

| Выходное напряжение низкого уровня | ≤ 0,4 В | |

| Выходное напряжение высокого уровня | ≥ 2,4 В | |

| Напряжение на антизвонном диоде | ≥ -1,5 В | |

| Помехоустойчивость | ≤ 0,4 В | |

| Входной ток низкого уровня | ≤ -1,6 мА | |

| Входной ток высокого уровня | ≤ 0,04 мА | |

| Входной пробивной ток | ≤ 1 мА | |

| Ток короткого замыкания | -18...-55 мА | |

| Ток потребления при низком уровне выходного напряжения | ≤ 11 мА | |

| Ток потребления при высоком уровне выходного напряжения | ≤ 4 мА | |

| Потребляемая статическая мощность на один логический элемент | ≤ 19,7 мВт | |

| Выходной ток низкого уровня | ≤ 16 мА | |

| Время задержки распространения при включении | ≤ 15 нс | |

| Время задержки распространения при выключении | ≤ 22 нс |

Зарубежные аналоги: SN7420

Вывод

В результате выполнения задания получены навыки по работе со справочной литературой. Обработано несколько источников информации. Получены сведения по электрическим характеристикам для цифровых компонентов, составлены таблицы истинности.

2 Результат выполнения задания №2 «Генераторы и схемы

«Генераторы и схемы

задержки»

Задание:

Рассчитать генератор на частоту 32 КГц, построенного по принципу, как показано на рисунке 2.1.

– определить полный период сигнала;

– определить номиналы конденсатора и резистора.

На рисунке 2.1 представлена электрическая схема генератора.

Рисунок 2.1 – Схема RC генератора

В таблице 2.2 приведены расчетные параметры генератора.

Таблица 2.2 – Расчетные параметры генератора

| R1,(КОм) | C1 | Т,нс | F, КГц |

| 35(pF) | 60,264 | ||

| 350(pF) | 47,081 | ||

| 35(nF) | 47,081 | ||

| 350(nF) | 45,198 | ||

| 35(mF) | 1,902 | ||

| 350(mF) | 3,710 |

На рисунке 2.2 представлены схемы формирования задержек.

Рисунок 2.2 – Схемы формирования задержек

В таблице 2.3 приведены расчетные параметры цепи задержки.

Таблица 2.3 – Расчетные параметры цепи задержки

| tЗ, нс | Количество лог. Элементов, n |

| 82,863 | |

| 60,264 | |

| 45,198 | |

| 30,132 |

|

Вывод

Согласно заданию требуется рассчитать показатели генератор на частоту 32 КГц,определить полный период сигнала, определить номиналы конденсатора и резистора.

В результате выполнения задания проведен синтез компонентов как показано на рисунке 2.1, проведена отладка и проверка работоспособности схемы.

Измерены параметры генератора и параметры цепи задержки. В ходе выполнения работы сделан вывод, что увеличение номиналов конденсатора и резистора, делает работу генератора некорректной или недопустимой.

3 Результат выполнения задания №3 «Восьмиразрядное АЛУ»

Задание:

– построить схему 8 разрядного АЛУ;

– операция: сложение и вычитание;

– применяются 2 регистра;

– шина данных общая разделяемая;

– результат операции заносится в первый регистр;

– результат с первого регистра возвращается в шину данных;

– управление шины данных осуществить с применением буферных формирователей;

В приложении А (ОП 230113.13.01.23 Э3) представлена электрическая схема 8-ми разрядного АЛУ.

В приложении А (ОП 230113.13.01.23 Э3) представлена электрическая схема 8-ми разрядного АЛУ.

Вывод

Согласно заданию требуется построить схему 8 разрядного АЛУ, в котором будет выполняться операция сложения и вычитания.

В результате выполнения задания проведена разработка схемы 8 разрядного АЛУ, описаны цифровые компоненты схемы с использованием справочников; проанализирована операция сложения и вычитания.

4 Результат выполнения задания №4 «Проектирование цифровых устройств в системе Quartus II»

4 Результат выполнения задания №4 «Проектирование цифровых устройств в системе Quartus II»

Задание:

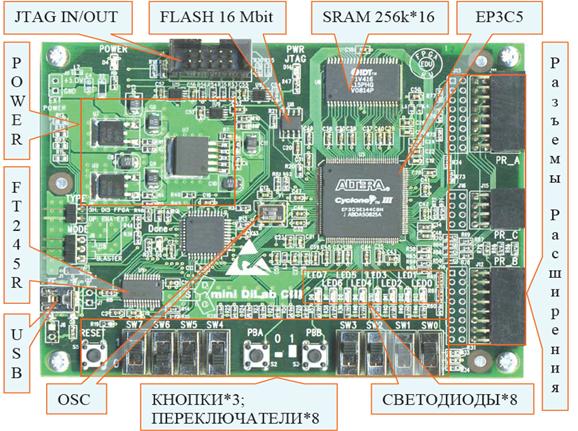

Ознакомление с устройством, характеристиками отладочной платы mini- DiLaB (Cyclone 3).

На рисунке 4.1 представлен внешний вид отладочной платы mini- DiLaB.

Рисунок 4.1 – Внешний вид mini- DiLaB (Cyclone 3)

Как видно из рисунка 4.1 по функциональному набору периферийных компонентов, данный стенд уступает DiLab II, за кажущейся простотой скрывается достаточно, мощное устройство, не обременяющее разработчика излишней обвязкой периферийных устройств. Данный стенд позволяет сосредоточится на решении конкретных задач. Необходимый набор устройств и компонентов подключается посредством портов расширения.

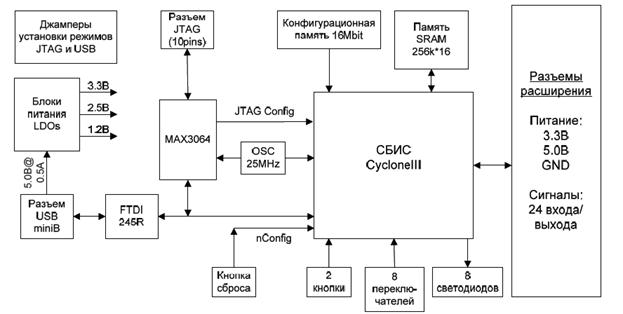

На рисунке 4.2 представлена структурная схема устройства.

Рисунок 4.2– Структурная схема стенда

В состав комплекса входят:

– СБИС Программируемой Логики (Cyclone III);

– конфигурационная память СБИС Cyclone III;

– переключатели;

– кнопки ввода данных;

– светодиоды (8 доступных программисту);

– микросхема статической памяти (объемом 256k*16 бит);

– кварцевый генератор;

– USB интерфейс, включающий:

1) разъем miniB;

2) микросхему FTDI - FT245R ;

;

– JTAG интерфейс, включающий:

1) микросхему MAX3064;

2) набор джамперов для выбора режима работы;

3) разъем JTAG;

– разъемы расширения;

– модуль питания платы.

Центральным элементом стенда является микросхема EP3C5E144C8N. Данная ПЛИС имеет следующие характеристики:

Число выводов СБИС – 144;

- число пользовательских выводов (входов/выходов) – 94;

- Число логических элементов – 5136;

- Объем встроенной памяти – 414 кбит;

- Число встроенных умножителей ( разрядностью 9*9) – 46;

- Число встроенных умножителей тактовых сигналов (PLL) – 2;

- Объем файла конфигурации (без сжатия) – 3 Мбит.

Примечание: на плате присутствует кнопка RESET, позволяющая сбросить текущую конфигурацию СБИС.

Плата miniDiLaB-CIII содержит 8 переключателей. В положении «1» переключатель коммутирует логическую единицу, а в положении «0» - логический нуль. Верхнее положение – лог. «1», в нижнем - «0».

На рисунке 4.3 представлены переключатели платы miniDiLaB-CIII.

Рисунок 4.3– Переключатели платы miniDiLaB-CIII

Рисунок 4.3– Переключатели платы miniDiLaB-CIII

Плата miniDiLaB-CIII содержит 2 кнопки: при нажатой кнопке передается логический «0», при отжатой – логическая «1».

Плата miniDiLaB-CIII содержит 2 кнопки: при нажатой кнопке передается логический «0», при отжатой – логическая «1».

На рисунке 4.4 представлены кнопки платы miniDiLaB-CIII.

.

.

Рисунок 4.4– Кнопки платы miniDiLaB-CIII

Плата miniDiLaB-CIII содержит 8 светодиодов.

На рисунке 4.5 представлены светодиоды для индикации платы miniDiLaB-CIII.

Рисунок 4.5– 8 светодиодов для индикации

|

5 Результат выполнения задания №5 «Проектирование цифровых

устройств в системе Quartus II. Бегущий огонь»

Цель: самостоятельно пройти процесс проектирования от постановки задачи, до реализации работающего устройства.

Задача: спроектировать цифровое устройство выполняющее, поочередное включение/выключение светодиодов.

Дать ответ на вопросы:

Дать ответ на вопросы:

1. Назначение выводов Carry –out, Set, Load у счетчиков

2. Как изменить код описания счетчика-дешифратора, чтобы «бегущий огонь» начинался с led 7 и шел до led 0 (ответ в виде части кода в отчете)

Алгоритм работы

- деление на счетчике частоты 25Mhz на 2**23; - поочередное включение (активный уровень – логический нуль)/выключение… В САПР Quartus II создать новый проект.Результат выполнения задания №6

«Проектирование цифровых устройств в системе Quartus II. Генератор псевдослучайных последовательностей»

Цель: самостоятельно пройти процесс проектирования от постановки задачи, до реализации работающего устройства.

Задача: спроектировать цифровое устройство выполняющее, формирование псевдослучайных последовательностей (генератор случайных чисел).

Описание:

Разрабатываемое устройство позволяет переходить в один момент времени в состояние (формировать уникальный двоичный код).

Алгоритм работы:

- установлено некое начальное число (обратная связь);

- при нажатии кнопк «PB_A» c тактового генератора поступает серия синхроимпульсов на вход сдвиговых регистров.

- случайным образом выбранные выходы с регистров объединены логическими элементами «mod2», выход с элементов заведен на последовательный вход сдвигового регистра.

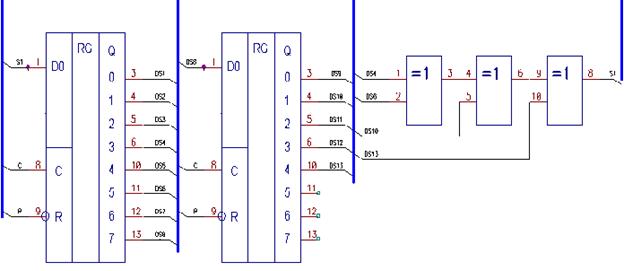

На рисунке 6.1 представлена схема, реализующая формирование псевдослучайных последовательностей.

Рисунок 6.1– Схема формирования псевдослучайных последовательностей.

Рисунок 6.1– Схема формирования псевдослучайных последовательностей.