Принципы аналого-цифрового преобразования

Параллельный преобразователь

В параллельном преобразователе (рис. 10.1) входной сигнал подается сразу на множество компараторов, осуществляющих сравнение сигнала с опорными напряжениями. Опорные напряжения формируются цепочкой резисторов, делящих эталонное напряжение Uo на равные части.

|

Рис. 10.1. Параллельный аналого-цифровой преобразователь. Такие схемы ADC

работают очень быстро, но сложны и используются редко.

Преобразователь последовательного приближения

Основными элементами преобразователя (рис. 10.2) является регистр последовательных приближений, код из которого с помощью цифроаналогового преобразователя преобразуется в напряжение. Компаратор CMP сравнивает входное напряжение с выходным напряжением преобразователя и через устройство управления воздействует на регистр.

|

Рис. 10.2. Преобразователь последовательного приближения

Преобразование выполняется за несколько тактов. В первом такте в старший разряд регистра последовательных приближений записывается единица. Если в результате сравнения на выходе компаратора устанавливается единичный сигнал, единица в старшем разряде регистра сохраняется. В противном случае - сбрасывается. Далее, в том же порядке, формируется второй по старшинству разряд результата, потом - третий и т.д. Для получения результата необходимо n тактов, где число n равно разрядности преобразователя.

Интегрирующий преобразователь

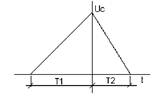

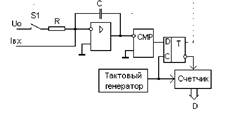

Интегрирующий ADC для сравнения входного сигнала с эталонным использует заряд конденсатора. Сначала (рис. 10.3) конденсатор в течении фиксированного промежутка времени Т1 заряжается током, пропорциональным входному сигналу. После это он разряжается постоянным током с определенным значением. Время разряда конденсатора Т2 пропорционально значению входного напряжения. Оно фиксируется с помощью счетчика и поступает на выход схемы (рис. 10.4).

|

Рис. 10.3. Интегрирование сигнала в преобразователе

Интервал времени 77 задается включением ключа S1. По окончании Т1 ключ S1 размыкается, a S2 - замыкается. Опорное напряжение Uo должно иметь знак противоположный знаку напряжения входного. Компаратор, устройство управления и счетчик определяют выходной код D, пропорциональный интервалу T2.

|

Рис. 10.4. Интегрирующий ADC

Интегрирующие схемы ADC имеют 8-16 разрядов и могут представлять результат в двоичном или двоично-десятичном коде.

Сигма-дельта преобразователь

Сигма-дельта преобразователи являются разновидностью интегрирующих ADC, в которых входной ток компенсируется коммутируемым зарядом от встроенного источника (рис. 10.5). Импульсы тока фиксированной длительности на каждом такте могут быть подключены к входу интегратора. В суммирующей точке интегратора поддерживается нулевой средний ток. Счетчик подсчитывает количество импульсов, поступающих в суммирующую точку за фиксированный период времени. Результат счета пропорционален входному напряжению.

|

Рис. 10.5. Сигма-дельта преобразователь