Интерфейс UART

Асинхронный последовательный интерфейс UART (Universal Asynchronous Receiver Transmitter - универсальный асинхронный приемопередатчик) обеспечивает полудуплексный режим обмена по трем линиям. В обмене всегда участвуют только два устройства, одно из которых является передатчиком, второе- приемником.

В режиме асинхронной передачи каждое слово данных передается автономно и передача может быть начата в любой момент времени. Стандартный формат асинхронной передачи изображен на рис. 13.1.

|

Рис. 13.1. Формат асинхронной передачи

Передача начинается со стартового (нулевого) бита. Затем передается от 5 до 8 бит данных. Передача заканчивается необязательным битом четного (или нечетного) паритета и одним (полутора или двумя) единичными стоповыми битами. После этого в любой момент времени может быть начат цикл передачи следующего слова.

Подразумевается, что приемник и передатчик работают на одной скорости, измеряемой числом бит в секунду (бод). Внутренний генератор синхронизации приемника запускается при обнаружении стартового бита. В идеальном случае эти импульсы располагаются в середине битовых интервалов.

Формат асинхронной передачи позволяет выявлять возможные ошибки:

0 если обнаружен стартовый бит и генератор синхронизации запущен, а по первому импульсу синхронизации фиксируется уровень логической единице, стартовый бит считается ложным;

0 если по импульсам синхронизации, соответствующим стоп-битам, в приемнике фиксируется логический нуль, сообщение считается ошибочным (ошибка кадра);

0 если контрольный бит не соответствует принятому соглашению о паритете, фиксируется ошибка паритета.

Контроль формата позволяет обнаружить обрыв линии по отсутствию стоп-бита. Для асинхронной передачи принят стандартный ряд скоростей: 50, 75,110,150, 300, 600,1200, 2400,4800, 9600,19200, 38400, 57600,115200 бит/с:

В простейшем случае асинхронный приемопередатчик имеет две сигнальные линии:

0 TxD (Transmit Data)- выход,

0 RxD (Receive Data) - вход,

При этом два устройства-приемопередатчика должны быть соединены между собой тремя линями, или так называемым нуль-модемным кабелем (рис.13.2).

|

Рис. 13.2. Нуль-модемный кабель

Управление UART

Управление UART осуществляется через регистры ввода/вывода. В контроллере ATmega163 для управления используется 5 регистров (рис. 13.3):

0 Регистр UDR (UART Data Register) - регистр данных UART

0 Регистр UCSRA (UART Control and Status Register A) -регистр А управления и статуса UART

0 Регистр UCSRB (UART Control and Status Register B) - регистр В управления и статуса UART

0 Регистры UBRRH1 и UBRR (UART Baud Rate registers) - регистры скорости передачи.

|

Рис.13.3. Регистры UART

Регистр данных UDR (UART Data Register) физически является двумя регистрами: регистром передачи данных и регистром приема данных, использующими одни и те же адреса $0C ($2C). При записи в регистр запись производится в регистр передачи данных UART, при чтении происходит чтение содержимого регистра приема данных UART.

Скорость обмена данными в UART задается с помощью бод-генератора (Baud Rate Generator). Он представляет собой делитель, генерирующий импульсы синхронизации с

частотой, определяемой выражением:

|

где

0 BAUD = частота в бодах (бит/сек),

0 CK = частота кварцевого генератора,

0 UBRR = содержимое 12-битного регистра UBRR (UART Baud Rate register).

Физически 12-битный регистр UBRR размещается в двух 8-битных регистрах. Младшие 8 бит в регистре UBRR, старшие 4 бита - в регистре UBRRH1 (рис. 13.3).

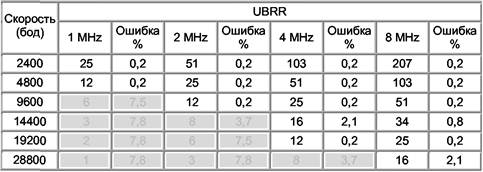

При использовании стандартных кварцевых резонаторов, наиболее часто используемые скорости передачи в бодах могут быть получены установками UBRR, представленными в таблице 13.1. При установках UBRR, указанных в таблице, реальные скорости в бодах будут иметь отличия менее 2% от стандартных скоростей.

Таблица 13.1. Установки UBRR при стандартных частотах синхронизации

Таблица 13.1. Установки UBRR при стандартных частотах синхронизации

|

Фактически, для регулирования скорости передачи UART достаточно только одного регистра UDDR. В регистр UDDRH1 во всех рассмотренных случаях записывается константа $00.

Передатчик

Блок-схема передатчика UART показана на рис. 13.3.

|

Рис. 13.3. Передатчик UART

Установленный в состояние 1 бит TXEN регистра UCSRB разрешает передачу данных UART. Передача инициируется записью передаваемых данных в регистр данных UDR. Данные пересылаются из UDR в сдвиговый регистр передачи в следующих случаях:

0 Новый символ записан в UDR после того как был выведен из регистра столовый бит предшествовавшего символа. Сдвиговый регистр загружается немедленно.

0 Новый символ записан в UDR прежде, чем был выведен столовый бит предшествовавшего символа. Сдвиговый регистр загружается после выхода стопового бита передаваемого символа, находившегося в сдвиговом регистре.

Если из 10(11)-разрядного сдвигового регистра передачи выведена вся информация (сдвиговый регистр передачи пуст) данные из UDR пересылаются в сдвиговый регистр. В это время устанавливается бит UDRE (UART Data Register Empty) регистра статуса USR (UART Status Register). При установленном в состояние 1 бите UDRE приемопередатчик готов принять следующий символ. Запись в UDR очищает бит UDRE. В то самое время, когда данные пересылаются из UDR в 10(11)-разрядный сдвиговый регистр, бит 0 сдвигового регистра сбрасывается в состояние 0 (состояние 0 - стартовый бит) а бит 9 или 10 устанавливается в состояние 1 (состояние 1 - столовый бит). Если в регистре управления UCSRB установлен бит CHR9 (т.е. выбран режим 9-разрядного слова данных), то бит TXB8 регистра UCSRB пересылается в бит 9 сдвигового регистра передачи. Сразу после пересылки данных в сдвиговый регистр тактом бод-генератора стартовый бит сдвигается на вывод TxD. За ним следует LSB данных. Когда будет выдан столовый бит сдвиговый регистр загружается новой порцией данных, если она была записана в UDR во время передачи. В процессе загрузки бит UDRE находится в установленном состоянии. Если же новые данные не будут загружены в UDR до выдачи стопового бита, флаг UDRE остается установленным. В этом случае, после того как столовый бит будет присутствовать на выводе TxD в течение одного такта, в регистре управления и статуса UCSRA устанавливается флаг завершения передачи TxC (TX Complete Flag).

Приемник

Структурная схема приемника UART приведена на рис. 13.4.

|

Рис. 13.4. Приемник UART

Логика восстановления данных (Front-End Logic) производит выборку состояний вывода RxD с частотой в 16 раз большей, чем частота передачи. При нахождении линии в пассивном состоянии одиночная выборка нулевого логического уровня будет интерпретироваться как падающий фронт стартового бита и будет запущена последовательность детектирования стартового бита. Считается, что первая выборка обнаружила первый нулевой логический уровень вероятного стартового бита. На выборках 8, 9 и 10 приемник вновь тестирует вывод RxD на изменение логических состояний. Если две или более из этих трех выборок обнаружат логические 1, то данный вероятный стартовый бит отвергается как шумовой всплеск и приемник начнет выявлять и анализировать следующие переходы из 1 в 0.

Если же был обнаружен действительный стартовый бит, то начинает производиться выборка следующих за стартовым битом информационных битов. Эти биты также тестируются на выборках 8,9 и 10. Логическое состояние бита принимается по двум и более (из трех) одинаковым состояниям выборок. Все биты вводятся в сдвиговый регистр приемника с тем значением, которое было определено тестированием выборок.

Тестирование выборок битов принимаемых символов показано на рис. 13.5.

Рис. 13.5. Тестирование выборок принимаемых данных

При поступлении стопового бита необходимо, чтобы не менее двух выборок из трех подтвердили прием стопового бита (показали высокий уровень). Если же две или более выборок покажут состояния 0, то при пересылке принятого байта в UDR в регистре управления и статуса UCSRA устанавливается бит ошибки кадра FE (Framing Error). Для обнаружения ошибки кадра пользователь перед чтением регистра UDR должен проверять состояние бита FE. Флаг FE очищается при считывании содержимого регистра данных UART (UDR).

Вне зависимости от того принят правильный столовый бит или нет, данные пересылаются в регистр UDR и устанавливается флаг RXC в регистре управления UCSRA. Регистр UDR фактически является двумя физически отдельными регистрами, один из которых служит для передачи данных и другой для приема. При считывании UDR обращение ведется к регистру приема данных, при записи обращение ведется к регистру передачи. Если выбран режим обмена 9-разрядными словами данных (установлен бит CHR9 регистра UCR), при пересылке данных в UDR бит RXB8 регистра UCR загружается из девятого бита сдвигового регистра передачи. Если после получения символа к регистру UDR не было обращения, начиная с последнего приема, в регистре UCSRA устанавливается флаг переполнения OR. Это означает, что новые данные, пересылаемые в сдвиговый регистр, не могут быть переданы в UDR и потеряны. Бит OR буферирован и доступен тогда, когда в UDR читается байт достоверных данных. Пользователю, для обнаружения переполнения, необходимо всегда проверять флаг OR после считывания содержимого регистра UDR.

При очищенном (сброшенном в логическое состояние 0) бите RXEN регистра UCR прием запрещен.

Мультипроцессорный режим обмена

Мультипроцессорный режим позволяет данные от одного ведущего контроллера передать нескольким подчиненным (ведомым) контроллерам. Это осуществляется декодированием первого адресного байта, позволяющего выяснить, который из подчиненных контроллеров адресован. Если подчиненный контроллер адресован, он примет следующие байты данных, в то время как другие подчиненные контроллеры игнорируют эти байты данных до получения другого адресного байта.

Для ведущего контроллера необходимо ввести 9-разрядный режим передачи (CHR9 в регистре UCSRB установлен). 9-ый бит должен быть равен 1, если передается адресный байт, и нулю, если передается байт данных.

Для ведомых контроллеров, механизм проявляется слегка по-другому для 8- разрядного и 9-разрядного режима приема. В 8-разрядном режиме приема (CHR9 в регистре UCSRB сброшен), столовый бит равен 1 для адресного байта и нулю - для байта данных. В 9-разрядном режиме приема (CHR9 регистре UCSRB установлен), 9-ый бит равен 1 для адресного байта и нулю - для байта данных, принимая во внимание, что столовый бит - всегда равен 1.

В мультипроцессорном режиме обмена должна использоваться следующая процедура:

0 Все подчиненные контроллеры переводятся в мультипроцессорный режим связи (устанавливается бит MPCM в регистре UCSRA).

0 Ведущий контроллер посылает адресный байт, и все ведомые принимают и читают этот байт (флажки RXC в регистрах UCSRA устанавливаются).

0 Каждый ведомый контроллер читает свой регистр UDR и определяет был ли он выбран. Если так, то он очищает MPCM бит в регистре UCSRA, и далее ожидает байт данных.

0 Для каждого полученного байта данных, принимающий контроллер устанавливает флажок RXC в регистре UCSRA. В 8-разрядном режиме, принимающий контроллер также генерирует ошибку кадровой синхронизации (FE в регистре UCSRA), начиная с нулевого стопового бита. Другие контроллеры, у которых бит MPCM равен 1, игнорируют байт данных. В этом случае, регистр UDR и бит RXC или FE не работают.

0 После передачи последнего байта повторяется процесс пересылки адреса.

Регистры управления UART

Регистр UCSRA

0 Бит 7 - RXC (UART Receive Complete) прием завершен. Данный бит устанавливается в состояние 1 при пересылке принятого символа из сдвигового регистра приема в UDR. Бит устанавливается вне зависимости от отсутствия или наличия ошибок приема кадра. При установленном в регистре UCSRB бите RXCIE и установленном бите RXC выполняется прерывание по завершению приема UART. Бит RXC очищается при считывании UDR. При приеме данных инициированном прерыванием, подпрограмма обработки прерывания по завершению приема UART должна считать UDR, с тем, чтобы очистить RXC, иначе по окончании подпрограммы обработки прерывания произойдет новое прерывание.

0 Бит 6 - TXC (UART Transmit Complete) - передача завершена. Данный бит устанавливается в состояние 1 когда весь символ (включая столовый бит) выведен из сдвигового регистра передачи и в UDR не записаны новые данные. Этот флаг используется при полудуплексном связном интерфейсе, когда оборудование передачи должно установить режим приема и освободить коммуникационную шину сразу после завершения передачи. При установленном бите TXCIE установка TXC приведет к выполнению прерывания по завершению передачи UART. Флаг TXC очищается аппаратно при выполнении обработки соответствующего вектора прерывания. Очистить бит TXC можно записью логической 1.

0 Бит 5 - UDRE (UART Data Register Empty) - регистр данных пуст. Данный бит устанавливается в состояние 1 когда символ, записанный в UDR, пересылается в сдвиговый регистр передачи. Установка этого бита означает, что передатчик готов к получению нового символа для передачи. Когда бит UDRIE установлен, до тех пор пока установлен UDRE, выполняется прерывание по завершению передачи UART. Бит UDRE очищается при записи в UDR. При приеме данных инициированном прерыванием, подпрограмма обработки прерывания по пустому регистру данных UART должна считать UDR, с тем, чтобы очистить UDRE, иначе по окончании подпрограммы прерывания произойдет новое прерывание. Во время сброса бит UDRE устанавливается в состояние 1 с тем, чтобы индицировать готовность передатчика.

0 Бит 4 - FE (Framing Error) ошибка кадра. Данный бит устанавливается в состояние 1 при обнаружении условий ошибочного приема кадра, т.е. когда столовый бит входящего символа в состоянии 0. Бит FE очищается при приеме стопового бита с логическим уровнем 1.

0 Бит 3 - OR (Over Run) - переполнение данных. Бит OR устанавливается в состояние 1 при обнаружении условий переполнения, т.е. когда символ, уже находящийся в регистре UDR, не считан перед пересылкой нового символа из сдвигового регистра приема. Бит OR буферирован, что означает, что он будет оставаться установленным пока не будут считаны правильные данные из UDR. Бит OR очищается (сбрасывается в 0) когда данные приняты и пересланы в UDR.

0 Бит 1 - U2X (Double UART Transmission Speed) - удвоение скорости передачи. Установка этого бита приводит к изменению коэффициента деления с 16 на 8, что эквивалентно удвоению скорости передачи.

0 Бит 0 - MPCM (Multi-processor Communication Mode) - режим мультипроцессорного обмена. При установке этого бита ведомый контроллер принимает адресный байт.

Регистр UCSRB

0 Бит 7 - RXCIE (RX Complete Interrupt Enable) - разрешение прерывания по завершению приема. При установленном в состояние 1 бите RXCIE и установленном разрешении глобального прерывания установка бита RXC в регистре UCSRA приведет к выполнению прерывания по завершению приема.

0 Бит 6 - TXCIE (TX Complete Interrupt Enable) - разрешение прерывания по завершению передачи. При установленном в состояние 1 бите TXCIE и установленном разрешении глобального прерывания установка бита TXC в регистре UCSRA приведет к выполнению прерывания по завершению передачи.

0 Бит 5 - UDRIE (UART Data Register Empty Interrupt Enable) - Разрешение прерывания по пустому регистру данных. При установленном в состояние 1 бите UDRIE и установленном разрешении глобального прерывания установка бита UDRE в регистре USR приведет к выполнению прерывания по пустому регистру данных UART.

0 Бит 4 - RXEN (Receiver Enable) - разрешение приемника. Установленный в состояние 1 бит RXEN разрешает приемник UART. Если приемник запрещен, то флаги статуса TXC, DOR и FE установить невозможно. Если эти флаги установлены, то очистка бита RXEN не приведет к очистке этих флагов.

0 Бит 3 - TXEN (Transmitter Enable) - разрешение передатчика. Установленный в состояние 1 бит TXEN разрешает передатчик UART. При запрещении передатчика во время передачи символа, передатчик не будет заблокирован прежде, чем будут полностью переданы символ в сдвиговом регистре плюс любой находящийся в UDR следующий символ.

0 Бит 2 - CHR9 (9 Bit Characters) - режим 9-разрядных символов. При установленном в состояние 1 бите CHR9 передаются и принимаются 9 - разрядные символы плюс стартовый и столовый биты. Девятые биты читаются и записываются с использованием битов RXB8 и TXB8 (соответственно) регистра UCSRA. Девятый бит данных может использоваться как дополнительный столовый бит или бит контроля четности.

0 Бит 1 - RXB8 (Receive Data Bit 8) - прием 8-разрядных данных. При установленном в состояние 1 бите CHR9 бит RXB8 является девятым битом данных принятого символа.

0 Бит 0 - TXB8 (Transmit Data Bit 8) - передача 8-разрядных данных. При установленном в состояние 1 бите CHR9 бит TXB8 является девятым битом данных передаваемого символа.

Программирование UART

При программировании UART в простейшем случае решаются три задачи: инициализация 11Ат~(задание режимов работы), организация приема данных и организация передачи данных. Примером инициализирующей подпрограммы может быть следующая последовательность команд:

.deftmp=r20 Init_uart: ldi tmp,0b00011101 ; Инициализация UART

out UCR,tmp ;TXEN=1 ,RXEN=1 ,CPH9=1 ,TXB8=1

ldi tmp,25 ;9600 бит/с при fclk=4МГц

out UBRR,tmp ret

Если микропроцессор использует последовательный канал для коротких однобайтных сообщений, то передавать и принимать данные можно, просто опрашивая флаги готовности передатчика и приемника UART. При передаче байта в последовательный канал все, что должен сделать процессор - дождаться установки флага готовности передатчика UDRE и записать затем передаваемый символ в регистр данных передатчика:

trans: sbis USR, UDRE ;Если бит UDRE в USR установлен, то пропустить

;следующую команду

rjmp trans ;Вернуться на метку trans

out UDR, r15 ;Вывести в регистр данных передатчика

UART ;содержимое r15 ret

Во время приема данных, очевидно, регистр данных приемника UART необходимо считывать лишь тогда, когда установлен флаг готовности RXC. Например:

receive: sbis USR, RXC ;Если бит UDRE в USR установлен, то пропустить

;следующую команду

rjmp receive ;Вернуться на метку receive

in r15, UDR ;Считать регистр данных приемника в г15

ret

Или, например, так: receive: sbic USR, RXC

; Если бит RXC в USR установлен, то пропустить

;следующукэ команду

in r15, UDR ;Считать регистр данных приемника UART в r15ret

В первом случае бесконечный цикл опроса флага RXC приведет к "зависанию" процессора, если ожидаемые данные так и не поступят на вход UART. Поэтому во второй подпрограмме предлагается не ждать бесконечно долго готовности приемника, а лишь один раз опросить флаг RXC. В случае, если он установлен, считать байт из регистра данных приемника, если нет - не считывать, но затем в любом случае завершить подпрограмму.

Описанные выше программы очень просты, но чрезвычайно неэффективны с точки зрения использования процессорного времени. Для передачи многобайтных сообщений процессорное ядро сможет быстро (за 0,25 мкс при Fck = 4МГц) записать в передатчик только первые два байта, а затем в течение интервала времени передачи байта в последовательный канал (при скорости 9600 бод передача одного байта занимает ~1ms) необходимо, опрашивая флаг готовности передатчика, ждать освобождения UART.

В этом отношении более рациональны программы, в которых взаимодействие быстрого процессорного ядра и медленного UART организуется с использованием системы прерываний. Пример такой организации программ для передачи данных по последовательному каналу можно найти на сайте www.atmel.ru.