рефераты конспекты курсовые дипломные лекции шпоры

- Раздел Программирование

- /

- Вид работы: Лекции

- /

- Адресация памяти

Реферат Курсовая Конспект

Адресация памяти

Адресация памяти - Лекция, раздел Программирование, СИСТЕМНОЕ ПРОГРАММИРОВАНИЕ Микропроцессор Делит Адресное Пространство На Произвольное Количество Сегмент...

Микропроцессор делит адресное пространство на произвольное количество сегментов, каждый из которых содержит не более 64 Кб. Адрес первого байта сегмента всегда кратен 16 байтам и называется адресом сегмента (параграфом сегмента, номером сегмента). Для обращения к памяти внутри сегмента используется дополнительный адрес, называемый смещением, который указывает расположение байта относительно начала сегмента (относительный адрес или относительное смещение или исполнительный адрес). Адрес сегмента и смещение составляют логический адрес.

Физический адрес образуется с помощью объединения 16 разрядного адреса сегмента и 16 разрядного смещения. Если адрес сегмента сдвинуть влево на 4 бита и дополнить справа 4 нуля, то получится 20-разрядный базовый адрес сегмента. Если сложить базовый адрес сегмента с 16 разрядным смещением, то получится 20 разрядный физический адрес. Следовательно, адресуемая память составляет 220 байт = 1024 К = 1 М. Адрес сегмента - пятизначное шестнадцатеричное число, последняя цифра = нулю, так как адрес получается в результате умножения на 16. Смещение - четырехзначное шестнадцатеричное число. В памяти слово хранится в двух соседних байтах. Младший байт - младший адрес. Старший байт - старший адрес.

2.3.Внутренние регистры процессора

2.3.1.Регистры общего назначения

В микропроцессоре есть четыре 16-битных регистра общего назначения: AX, BX, CX, DX. Младший и старший байты регистров общего назначения доступны для работы и имеют свои уникальные имена: AL и AH, BL и BH, CL и CH, DL и DH соответственно. Регистры общего назначения в основном используются для временного хранения данных, особенно операндов арифметических операций. Данные регистры взаимозаменяемы, но тем не менее каждый из них имеет специальные функции:

AX - основной регистр, используемый в арифметических операциях над словом, также используется в операциях ввода/вывода и в некоторых операциях со строками.

AL - используется в аналогичных операциях над байтами, при преобразовании 10-х чисел и в операциях над ними.

AH - используется при умножении и делении байтов.

BX - используется при адресации данных.

CX - счетчик числа повторений циклов, номер позиции элемента данных при операциях сдвига и циклического сдвига на несколько битов.

DX - используется как расширение аккумулятора при операциях, дающих 32-разрядный результат и в операциях ввода/вывода.

Начиная с микропроцессора 80386, в дополнение к вышеперечисленным регистрам, существуют еще 32-разрядные регистры общего назначения EAX, EBX, ECX, EDX, младшим словом которых являются регистры AX, BX, CX, DX соответственно.

2.3.2.Сегментные регистры

Все сегментные регистры имеют размер 16 битов (слово).

CS - содержит адрес сегмента кода исполняемой программы.

SS - указывает на сегмент стека - область данных, предназначенную для временного хранения параметров и адресов, используемых программой.

DS - указывает на сегмент данных.

ES - указывает на дополнительный сегмент данных, используется при операциях с цепочками (если данные программы превышают 64 Кб).

Если программа не изменяет значения регистра CS, то размер ее кода не может превышать 64 Кб. Переключение адреса сегмента кода программы выполняется с помощью специальных команд JMP и CALL, когда управление передается на дальнюю метку или в дальнюю процедуру. Эти формы передачи управления неявно изменяют значение регистра CS и позволяют создавать программы любого размера.

Начиная с микропроцессора 80386, в дополнение к вышеперечисленным регистрам, существуют еще два регистра для адресации дополнительных сегментов данных FS и GS.

2.3.3.Регистры смещения

Микропроцессор содержит пять основных 16-битных регистров смещения:

SP и BP - содержат смещение в сегменте стека. SP-указывает на вершину стека, BP используется как базовый регистр для того, чтобы зафиксировать положение стека в какой-то момент времени и в дальнейшем адресоваться к данным, расположенным в стеке;

SI и DI в основном используются для формирования сложных адресов, состоящих из смещения начала блока данных в сегменте, и относительного смещения элемента данных внутри блока. При этом смещение начала блока обычно хранится в регистре BX или непосредственно в команде, а SI или DI задают смещение внутри блока. Кроме того, они участвуют в выполнении команд работы с цепочками;

IP - указывает на следующую выполняемую команду в сегменте кода, адрес ее хранится в CS. Программа не может явно получить или изменить значение этого регистра. Однако команды JMP и CALL неявно изменяют его значение, а также сохраняют его в стеке и восстанавливают из стека.

Начиная с микропроцессора 80386, в дополнение к перечисленным регистрам, существуют еще 32-разрядные регистры смещения ESP, EBP, ESI, EDI, EIP, младшее слово которых составляют регистры SP, BP, SI, DI и IP соответственно.

2.3.4.Регистр флагов

Для 16-разрядных микропроцессоров регистр флагов имеет размер 16 битов и использует в реальном режиме работы 9 флагов: 6-статусных флагов (отражают результаты арифметических и логических операций) и 3-управляющих флага (изменяют режим работы процессора).

Начиная с микропроцессора 80386 регистр флагов имеет размер 32-бита, но в реальном режиме используются тоже только 9 флагов из младшего слова:

CF - флаг переноса, указывает на арифметический перенос разряда. CF также может содержать значение бита, который при сдвиге или циклическом сдвиге вышел за границы регистра. CF=1, если перенос был (0 разряд).

PF - флаг четности, указывает на четность единичных разрядов в результате операции. Используется в основном в операциях обмена данными (2 разряд).

AF - вспомогательный флаг переноса, указывает на корректировку, необходимую при двоично-десятичных арифметических операциях (фиксирует факт переноса из младшего полубайта в старший полубайт). Упакованное число - 2 цифры в байте. В микропроцессоре нет десятичного сумматора. Сложение и вычитание десятичных чисел производится как сложение и вычитание двоичных чисел. Результат может быть неверным десятеричным числом, поэтому существуют команды преобразования результата в правильное десятеричное число. Чтобы это сделать, надо знать, был ли перенос (4 разряд).

ZF - флаг нуля. Указывает на нулевой результат или равенство при сравнении (6 разряд).

SF - флаг знака. Указывает на отрицательный результат в арифметической операции, логической, операциях сдвига или циклического сдвига (7 разряд).

OF - флаг переполнения. Указывает на арифметическое переполнение при операции (выход за пределы допустимых значений) (11 разряд).

TF - флаг трассировки (ловушки). Управляет одношаговыми операциями (при использовании отладчика), генерируя программные прерывания в конце каждой команды (8 разряд).

IF - флаг прерываний. Управляет разрешением и запретом прерываний от внешних устройств. Блокирует все прерывания, за исключением немаскируемых прерываний (NMI) (9 разряд).

DF - флаг направления. Управляет направлением влево и вправо в операциях со строками. При DF=1 микропроцессор уменьшает на 1 содержимое регистров индекса SI и DI после выполнения команды, а при DF=0 увеличивает на 1 содержимое регистра индексов (10 разряд).

Регистр флагов не имеет имени, однако, часто 16-разрядный регистр флагов называют FLAGS, а 32-разрядный регистр флагов - EFLAGS.

Формат 16-разрядного регистра флагов

| OF | DF | IF | TF | SF | ZF | AF | PF | CF |

2.4.Режимы адресации

Обычно выделяют семь режимов адресации, которые определяют способ вычисления смещения адреса операнда :

Регистровая адресация.

Непосредственная адресация.

Прямая адресация.

Косвенная регистровая адресация.

Базовая адресация.

Прямая адресация с индексированием.

Базовая адресация с индексированием.

2.4.1.Регистровая адресация.

При таком способе адресации значения операндов содержатся в регистрах. Допускаются операции с любыми регистрами, кроме регистра IP. Регистр CS не может являться операндом - приемником.

Примеры использования регистровой адресации:

MOV AX, CX

ADD AX, BX

2.4.2.Непосредственная адресация

При таком способе адресации операндом - источником является непосредственное значение (константа).

Пример использования непосредственной адресации:

MOV CX, 5 или K EQU -8

MOV CX, K

2.4.3.Прямая адресация

При прямой адресации смещение адреса операнда (исполнительный адрес) содержится в самой команде, например:

.data

T DB 3

.code

MOV AL, T

Т - имя ячейки памяти , значение которой загружается в регистр AX.

2.4.4.Косвенная регистровая адресация

В данном случае регистр содержит не значение операнд, а его смещение в памяти. При этом для адресации операнда могут использоваться регистры BX, DI и SI, если операнд берется из сегмента данных (DS). Регистр ВР используется для косвенной адресации, если операнд находится в сегменте стека (SS). При использовании команд работы с цепочками регистр DI всегда адресует операнд в дополнительном сегменте памяти (ES).

Начиная с микропроцессора 80386 для косвенной регистровой адресации могут быть использованы все 32-разрядные регистры общего назначения: EAX, EBX, ECX, EDX.

Примеры использования косвенной регистровой адресации:

MOV AX,[BX].

Смещение адреса может быть загружено в регистр при помощи операции OFFSET, а адрес сегмента - операцией SEG.

MOV BX, OFFSET T

MOV DS, SEG T

Если требуется, можно изменить адрес сегмента ячейки памяти, используя префикс сегмента, например:

MOV AX, ES:[BX] - пересылает в AX операнд, адрес которого складывается из содержимого регистров ES и BX.

2.4.5.Базовая адресация

При этом способе адресации смещение адреса операнда образуется как сумма:

[BX] + сдвиг, если операнд в сегменте данных(DS);

[BP] + сдвиг, если операнд в стеке (SS).

Базовый адрес массива (записи) помещается в регистр BX или BP, а сдвиг указывает на элемент относительно базы. Для доступа к разным записям или к элементам разных массивов внутри массива достаточно только перегрузить регистр BX (BP).

Примеры базовой адресации:

MOV AX, [BX] + 4

MOV AX, [BX + 4].

2.4.6.Прямая адресация с индексированием

При такой адресации смещение адреса операнда образуется как сумма значений смещения ячейки памяти и смещения в регистре SI или DI. Данный способ используется для доступа к массивам данных. Например:

.data

T DB 6, 5, 4, 3

MOV DI, 3

MOV AL, T[DI] - Загружает в AL 3-й элемент массива T, т.е. 4.

При операциях со строками регистр DI по умолчанию указывает на дополнительный сегмент данных (CS).

2.4.7.Базовая адресация с индексированием

Смещение адреса операнда образуется как сумма трех компонент:

BX + SI + сдвиг или BX + DI + сдвиг, если операнд находится в основном сегменте данных (DS),

BP + SI + сдвиг или BP + DI + сдвиг, если операнд находится в сегменте стека (SS).

Удобен для адресации двумерных массивов, когда BX или BP содержат смещение адреса начала массива, а в индексных регистрах и сдвиге - индексы элементов по строке и столбцу, например:

MOV AX, [BX + DI + 2]

MOV AX, [DI + BX + 2]

MOV AX, T[DI][SI]

2.5.Система команд микропроцессора

Система команд микропроцессора обычно делится на семь групп команд:

Команды пересылки данных.

Арифметические команды.

Логические команды или команды манипулирования битами.

Команды передачи управления.

Команды обработки строк (цепочные команды).

Команды управления процессором.

Команды прерывания.

2.5.1.Команды пересылки данных.

Перечень команд пересылки данных приведен в таблице 2.1.

Таблица 2.1. Перечень команд пересылки данных.

| Мнемоника команды | Описание команды |

| Общие | |

| MOV (переслать) | источник - приемник |

| MOVSX (c м/п 80386) | источник - приемник |

| MOVZX ( c м/п 80386) | источник - приемник |

| XCHG (обменять) | источник - приемник |

| PUSH (включить в стек) | источник - стек |

| POP (извлечь из стека) | стек - приемник |

| PUSHA (включить в стек все) | регистры - стек |

| POPA (извлечь из стека все) | стек - регистры |

| XLAT (преобразовать) | M[AL] > AL |

| Аккумуляторные (ввода-вывода) | |

| IN (ввести) | Порт à AL или AX |

| OUT (вывести) | AL или AX à порт |

| XLAT (преобразовать) | f(AL) à AL |

| Адресные | |

| LEA (смещение) | Смещение источника à регистр |

| LDS (загрузить полный адрес в регистр DS) | Источник, источник + 1 à регистр |

| Источник + 2, источник + 3 à DS | |

| LES (загрузить полный адрес в регистр ES) | Источник, источник + 1 à регистр |

| Источник + 2, источник + 3 à ES | |

| LSS (c м/п 80386) | |

| LFS (c м/п 80386) | |

| LGS (c м/п 80386) | |

| Флажковые | |

| LAHF (загрузить флажки в AH) | SF, ZF, AF, PF, CF à AH |

| SAHF (запомнить AH во флажках) | AH à SF, ZF, AF, PF, CF |

| PUSHF (включить в стек флажки) | Флаги à стек |

| POPF (извлечь из стека флажки) | Стек à флаги |

2.5.1.1. Общие команды.

Команда MOV - переслать данные, основная команда группы.

Команда MOV осуществляет пересылку байт, слов или двойных слов.

Форматы команды MOV приведены в таблице 2.2.

Таблица 2.2. Форматы команды MOV.

| Передача данных | Слово | Байт |

| Регистр в регистр | MOV AX, BX | MOV AH, BH |

| Операнд в регистр или память | MOV CX, 850 | MOV BL, 35 |

| MOV PW, 850 | MOV PB, 35 | |

| Память в регистр | MOV DX, PW | MOV CL, PB |

| Регистр в память | MOV PW, DX | MOV PB, CL |

| Регистр в сегментный регистр | MOV ES, BX | |

| Сегментный регистр в регистр | MOV AX, DS | |

| Сегментный регистр в память | MOV PW, CS |

Исключения:

Нельзя пересылать данные из одной ячейки памяти в другую.

Нельзя загрузить в регистр сегмента операнд с непосредственной адресацией.

Нельзя переслать значение одного регистра сегмента в другой.

Нельзя использовать регистры CS и IP в качестве приемника в команде MOV.

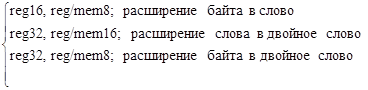

Команды MOVSX и MOVZX - новые команды пересылки данных, введенные в систему команд микропроцессора 80386. Форматы команд:

, где

, где

reg- только регистры общего назначения, mem - ячейка памяти.

MOVSX - пересылает данные и расширяет регистр знаковым разрядом операнда - источника,

MOVZX - пересылает данные и расширяет регистр нулями.

Команда XCHG - осуществляет обмен байт или слов. Один из ее операндов может быть в регистре или памяти, другой - в регистре. Различий между приемником и источником нет. Примеры использования команды прведены в таблице 2.3.

Таблица 2.3. Примеры использования команды XCHG.

| Обмен данными | Слово | Байт |

| Регистр с регистром | XCHG CX, DX | XCHG AL, AH |

| Регистр с памятью | XCHG BX, PW | XCHG BL, PB |

Исключение:

Нельзя выполнить обмен значений регистров сегментов.

– Конец работы –

Эта тема принадлежит разделу:

СИСТЕМНОЕ ПРОГРАММИРОВАНИЕ

СИСТЕМНОЕ ПРОГРАММИРОВАНИЕ КУРС ЛЕКЦИЙ ДЛЯ СТУДЕНТОВ ЗАОЧНОГО ФАКУЛЬТЕТА... САМАРА... УДК...

Если Вам нужно дополнительный материал на эту тему, или Вы не нашли то, что искали, рекомендуем воспользоваться поиском по нашей базе работ: Адресация памяти

Что будем делать с полученным материалом:

Если этот материал оказался полезным ля Вас, Вы можете сохранить его на свою страничку в социальных сетях:

| Твитнуть |

Хотите получать на электронную почту самые свежие новости?

Новости и инфо для студентов