рефераты конспекты курсовые дипломные лекции шпоры

- Раздел Высокие технологии

- /

- Захват, сравнение и широтно-импульсная модуляция

Реферат Курсовая Конспект

Захват, сравнение и широтно-импульсная модуляция

Захват, сравнение и широтно-импульсная модуляция - раздел Высокие технологии, АРХИТЕКТУРА МИКРОКОНТРОЛЛЕРА 16-Битный Таймер/счетчик Timer/counter1 Микроконтролле...

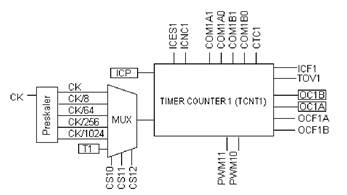

16-битный таймер/счетчик Timer/Counter1 микроконтроллера ATmega163 доступен процессорному ядру для чтения и записи, он может считать импульсы синхронизации CK, импульсы с выхода предделителя или импульсы с внешнего вывода Т1. При внешнем тактировании входной сигнал синхронизируется частотой тактового генератора СК. Для правильной работы таймера/счетчика 1 с внешним тактовым сигналом минимальное время между двумя переключениями внешнего этого сигнала должно быть не менее одного периода частоты синхронизации процессорного ядра.

Шесть 16-битных регистров счетчика/таймера обеспечивают хранение данных в режимах входного захвата, выходного сравнения и широтноимпульсной модуляции. Структурная схема таймера/счетчика 1 изображена на рис. 12.3.

|

Рис. 12.3. Таймер/счетчик 1 микроконтроллера ATmegal63

16-битный таймер счетчик считает импульсы со входа Т1 или тактовые импульсы СК. Переключением входа управляют биты CS10....CS12. При переполнении счетчика формируется флаг запроса на прерывание TOV1.

При воздействии на вход захвата содержимое счетчика копируется в специальный регистр захвата. В этом случае устанавливается флаг запроса на прерывание ICF1.

Содержимое счетчика в процессе работы сравнивается с содержимым специальных регистров сравнения. В момент равенства формируются флаги запросов на прерывания OCF1A и OCF1В и изменяются состояния выходов ОС1А и ОС1В.

В режиме широтноимпульсной модуляции счетчик считает от 0 до максимального значения. Далее направление счета меняется и отсчет ведется до нуля. Содержимое счетчика сравнивается с содержимым регистров сравнения. Результат сравнения отражается на выходах ОС1А и ОС1В.

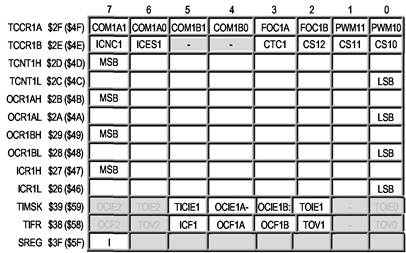

Работу счетчика обеспечивают 8-битные регистры, доступные процессорному ядру в пространстве регистров ввода/вывода (рис. 12.4):

0 регистры управления таймера счетчика TCCR1A (Timer/Counteri Control Register A) и TCCR1B (Timer/Counted Control Register B);

0 регистры данных TCNT1H (Timer/Counted High) и TCNT1L (Timer/Counteri Low);

0 регистры выходного сравнения OCR1AH (Timer/Counteri Output Compare Register A High) и OCR1AL (Timer/Counteri Output Compare Register A Low);

0 регистры выходного сравнения OCR1BH (Timer/Counteri Output Compare Register B High) и OCR1BL (Timer/Counted Output Compare Register B Low);

0 регистры входного захвата - ICR1H - (Timer/Counteri Input Capture Register High) и ICR1L (Timer/Counteri Input Capture Register Low);

0 регистр флагов прерывания TIFR (Timer/Counter Interrupt Flag Register),

0 регистр маски прерывания TIMSK (Timer/Counter Interrupt Mask Register),

0 регистр состояния микроконтроллера SREG (Status Register).

|

Рис.12.4. Регистры, участвующие в управлении таймером/счетчиком 1

В регистре масок прерываний TIMSK (Timer/Counter Interrupt Mask Register) устанавливаются разрешения/запрещения прерываний таймера/счетчика1:

0 Бит 5 - TICIE1 (Timer/Counteri Input Capture Interrupt Enable) - бит разрешения прерывания при срабатывании входа захвата.

0 Бит 4 - OCIE1A (Timer/Counteri Output CompareA Match Interrupt Enable) - бит разрешения прерывания при равенстве содержимого счетчика и содержимого регистра сравнения OCR1A.

0 Бит 3 - OCIE1B (Timer/Counteri Output CompareB Match Interrupt Enable) – бит разрешения прерывания при равенстве содержимого счетчика и содержимого регистра сравнения OCR1B.

0 Бит 2 - TOIE1 (Timer/Counteri Overflow Interrupt Enable) - бит разрешения прерывания при переполнении таймера/счетчика 1.

В регистре флагов прерываний T1FR (Timer/Counter Interrupt Flag Register) фиксируются события, являющиеся источниками прерываний:

0 Бит 5 - ICF1 (Input Capture Flag 1) - флаг прерывания при возникновении захвата.

0 Бит 4 - OCF1A (Output Compare Flag 1A) - флаг прерывания при равенстве содержимого счетчика и содержимого регистра сравнения OCR1A.

0 Бит 3 - OCF1B (Output Compare Flag 1B) - флаг прерывания при равенстве содержимого счетчика и содержимого регистра сравнения OCR1 В.

0 Бит 2 - TOV1 (Timer/Counteri Overflow Flag) - флаг прерывания при переполнении таймера/счетчика 1.

В регистре управления TCCR1B находятся биты для переключения входа счетчика/таймера 1.

0 Биты 2..0 - CS12, CS11, CS10 (Clock Select"!, Bit 2,1, and 0)

Таблица 12.2. Управление входом таймера/счетчика 1

| CS12 | CS11 | CS10 | Описание |

| Останов таймера/счетчика 1. | |||

| СК | |||

| CK/8 | |||

| CK/64 | |||

| СК / 256 | |||

| СК/1024 | |||

| Внешний контакт Т1, задний фронт импульса | |||

| Внешний контакт Т1, передний фронт импульса |

Регистры данных TCNT1H (Timer/Countert High) и TCNT1L (Jimer/Counteri Low) образуют 16-разрядный регистр, содержащий текущее значение 16-разрядного таймера/счетчика 1. Для того чтобы чтение/запись старшего и младшего байтов этого регистра происходило одновременно, обращение к ним реализовано посредством 8- разрядного регистра временного хранения (TEMP):

0 Если процессорное ядро производит запись в старший байт (TCNT1H), то записываемые данные размещаются в регистре TEMP. Затем, когда процессорное ядро производит запись в младший байт (TCNT1L) данные младшего байта объединяются с байтом данных регистра TEMP и все 16 битов одновременно переписываются в регистр таймера/счетчика TCNT1. Следовательно, при 16-разрядных операциях обращение к старшему байту (TCNT1H) должно выполняться первым. При использовании таймера/ счетчика1 в качестве 8-разрядного таймера достаточно производить запись только младшего байта.

0 Если CPU считывает младший байт (TCNT1L), то содержимое TCNT1L направляются непосредственно в процессорное ядро, а содержимое старшего байта (TCNT1H) размещается в регистре TEMP. При считывании старшего байта (TCNT1H) его содержимое будет изъято из регистра TEMP. Следовательно, при 16-разрядных операциях первым должно выполняться обращение к младшему байту (TCNT1L). При использовании таймера/счетчика1 в качестве 8-разрядного таймера достаточно производить запись только младшего байта.

Если основная программа и подпрограммы обработки прерываний используют обращение к регистрам посредством TEMP, то прерывания должны быть запрещены на время обращения из основной программы.

Таймер/счетчик 1 выполнен в виде суммирующего счетчика с возможностью чтения/записи. Если в таймер/счетчик1 занесено некоторое значение и выбран источник тактового сигнала, то он через один тактовый цикл продолжит счет с записанного значения.

Вход захвата

Функция захвата заключается в копировании содержимого таймера/счетчика 1 в регистр входа захвата ICR1. Процесс копирования запускается внешним событием на входе захвата ICP. Реальные установки захвата события определяются регистром управления таймером/счетчиком 1 TCCR1B (Timer/Counteri Control Register). Кроме того, для воздействия на вход захвата может быть использован аналоговый компаратор. Если разрешена функция подавления шума, действительные условия переключения события захвата тестируются, прежде чем захват будет активирован.

Регистры входа захвата ICR1H - (Timer/Counteri Input Capture Register High) и ICR1L (Timer/Counteri Input Capture Register Low) образуют 16-битный регистр ICR1, доступный только для чтения.

При обнаружении на входе захвата ICP нарастающего или падающего фронта сигнала (определяемого установкой бита ICES1) текущее состояние таймера/счетчика 1 пересылается в регистр входа захвата ICR1. Одновременно устанавливается в состояние 1 флаг захвата входа ICF1 (Input Capture Flag 1) в регистре флагов прерывания TIFR (Timer Interrupt Flags Register).

Поскольку регистр входа захвата ICR1 16-разрядный, то для обеспечения одновременного чтения его старшего и младшего байтов ICR1H и ICR1L используется регистр временного хранения TEMP. При считывании данных младшего байта содержимое ICR1L пересылается в процессорное ядро, а содержимое старшего байта ICR1H размещается в регистре TEMP. Чтение старшего байта заключается в переносе в процессорное ядро содержимого регистра временного хранения TEMP. Следовательно, при чтении всего 16-разрядного регистра операцию чтения необходимо начинать с младшего байта ICR1L. Регистр TEMP используется также при обращении к TCNT1, OCR1A и OCR1B. Если основная программа и подпрограммы обработки прерываний, используют обращение к регистрам посредством TEMP, то прерывания на это время должны быть запрещены. Для управления входом захвата используются отдельные биты регистра TCCR1B (Timer/Counteri Control Register B):

0 Бит 7 - ICNC1 (Input Capturei Noise Canceler) - установка режима подавления шума на входе захвата 1. При сброшенном в состояние 0 бите ICNC1 функция подавления шума входного триггера захвата запрещена. Вход захвата в этом случае реагирует на первый же импульс, поступивший на контакт входа захвата IC1. При установленном в состояние 1 бите ICNC1 импульс, поступивший на вход захвата IC1 подвергается серьезной проверке - состояние входа IC1 опрашивается последовательно четыре раза. Все четыре выборки должны иметь одинаковый (высокий/низкий), определяемый битом ICES1, уровень. Частота опроса соответствует частоте синхронизации процессорного ядра.

0 Бит 6 - ICES1 (Input Capturei Edge Select) - выбор фронта срабатывания на входе захвата 1. При сброшенном в состояние 0 бите ICES1 содержимое таймера/счетчика 1 пересылается в регистр захвата входа ICR1 по падающему фронту на входе захвата IC1. При установленном в 1 бите ICES1 содержимое таймера/счетчика1 пересылается в регистр захвата входа ICR1 по нарастающему фронту на входе захвата IC1.

Выходы сравнения

Таймер/счетчик 1 поддерживает два выхода сравнения, используя регистры сравнения выходов A и B - OCR1A и OCR1B в качестве источников данных, сравниваемых с содержимым таймера/счетчика 1. Функции сравнения включают очистку счетчика по совпадению сравнения A и воздействие на выходы сравнения выхода при двойном совпадении.

Регистры выходов сравнения OCR1AH (Timer/Counteri Output Compare Register A High), OCR1AL (Timer/Counteri Output Compare Register A Low), OCR1BH (Timer/Counteri Output Compare Register B High) и OCR1BL (Птег/Counteri Output Compare Register B Low) образуют два 16-разрядных регистра OCR1A и OCR1B.

Регистры OCR1A и OCR1B хранят данные, постоянно сравниваемые с состоянием таймера/счетчика 1. Действие, запускаемое совпадением при сравнении определяется содержимым регистра управления и состояния таймера/счетчика! Совпадение может произойти, только если таймер/счетчик 1 досчитает до значения содержимого OCR1A или OCR1B. Если в TCNT1 и OCR1A или OCR1B программно будут записаны одинаковые значения, то совпадение при сравнении сгенерировано не будет.

Совпадение при сравнении устанавливает флаг прерывания по совпадению в тактовом цикле процессорного ядра, следующем за самим совпадением.

Поскольку регистры сравнения выхода OCR1A и OCR1B являются 16-битными, то для обеспечения одновременного занесения старшего и младшего байтов данных в регистры OCR1A/B используется регистр временного хранения TEMP. Когда процессорное ядро записывает старший байт, то данные временно сохраняются в регистре TEMP. Когда же записывается младший байт в OCR1AL или OCR1BL, то одновременно содержимое регистра TEMP переписывается в OCR1AH или OCR1BH. Следовательно, при 16- разрядных операциях старшие байты регистров OCR1 A/B должны записываться первыми.

Кроме того, регистр TEMP используется при обращении к TCNT1 и ICR1. Если основная программа и подпрограммы обработки прерываний, используют обращение к регистрам посредством TEMP, то на это время прерывания должны быть запрещены. Для управления выходами захвата используются отдельные биты регистров TCCR1A и TCCR1B.

Регистр управления TCCR1A (Timer/Counter 1 Control Register A ):

0 Биты 7,6 - СОМ1А1, СОМ1А0 (Compare Output ModeiA, bits 1 and 0) - биты задания режима выхода. Определяют характер выходного сигнала при сравнении таймера/счетчика 1 с регистром OCR1A. Выходной сигнал поступает на выход ОС1А (Output Compare A). Конфигурирование управления представлено в таблице 12.3.

Таблица 12.3. Выбор режима сравнения

| СОМ1Х1 | СОМ1Х0 | Описание |

| Таймер/счетчик1 отключен от вывода ОС1Х | ||

| Переключение выходной линии ОС1Х | ||

| Очистка выходной линии ОС1Х (на линии низкий уровень) | ||

| Установка выходной линии ОС1Х (на линии высокий уровень) |

Примечание: X = A или B.

0 Биты 5,4 - СОМ1В1, СОМ1В0 (Compare Output ModeiB, bits 1 and 0) - биты задания режима выхода В. Биты определяют характер сигнала на выходе при сравнении таймера/счетчика 1 с регистром OCR1B. Сигнал выхода поступает на вывод ОС1В (Output Compare B). Конфигурирование управления представлено в таблице 5.13. При изменении битов СОМ1Х1/СОМ1Х0 прерывания по сравнению выхода 1 должны быть запрещены очисткой битов разрешения прерывания в регистре TIMSK. В противном случае при изменении битов может произойти прерывание

0 Бит 3 - FOC1A (Force Output CompareiA) - воздействие на выход ОС1А. Запись логической единицы в этот бит приводит к изменению на выводе ОС1А относительно значений установленных битами СОМ1А1 и СОМ1А0. Если СОМ1А1 и СОМ1А0 биты занесены в том же самом цикле, что и FOC1A, то новые значения не будут вступать в силу. Бит может использоваться, чтобы изменить состояние выхода OCR1A. При этом никакое прерывание не генерируется и таймер не очищается. FOC1A бит всегда читается как нуль.

0 Бит 2 - FOC1B (Force Output Compare 1В) воздействие на выход ОС1В. Запись логической единицы в этот бит приводит к изменению на выводе ОС1В относительно значений установленных битами СОМ1В1 и СОМ1В0. Если СОМ1В1 и СОМ1В0 биты занесены в том же самом цикле, что и FOC1B, то новые значения не будут вступать в силу. Бит может использоваться, чтобы изменить состояние выхода OCR1B. При этом никакое прерывание не генерируется и таймер не очищается. FOC1B бит всегда читается как нуль. Регистр TCCR1B - (Jlmer/Counteri Control Register B):

0 Бит 3 - СТС1 (Clear Timer/Counteri on Compare Match) - очистка таймера/счетчика 1 по совпадению. При установленном в состояние 1 бите СТС1 таймер/счетчик 1 при совпадении сбрасывается в состояние $0. Если бит СТС1 очищен, таймер/счетчик1 продолжает отсчет и не реагирует на совпадение при сравнении. Поскольку совпадение при сравнении детектируется в течение тактового цикла процессорного ядра следующего за совпадением, то поведение функции будет различно при различных коэффициентах предделителя. При коэффициенте предварительного деления 1 и установленном в регистре сравнения A состоянии C таймер будет считать в соответствии с установкой бита СТС1:. | С-1 | C | С+1 | 0 |1 | ... При установленном коэффициенте предварительного деления 8 таймер будет считать следующим образом:... | С-1, С-1, С-1, С-1, С-1, С-1, С-1, С-1 | C, C, C, C, C,C, C, C | С+1, 0, 0, 0, 0, 0, 0, 0, 0 | ….

Режим широтно-импульсной модуляции

Таймер/счетчик 1 может быть использован в качестве 8, 9 или 10-разрядного широтно-импульсного модулятора (PWM - Pulse Width Modulator). Работой PWM управляют отдельные биты регистра управления TCCR1A (Timer/Counterf Control Register A):

0 Биты 1,0 - PWM11, PWM10 (Pulse Width Modulator Select Bits) - биты выбора режима широтно-импульсной модуляции. Данные биты определяют установку режима ШИМ, как это показано в таблице 12.4.

Таблица 12.4. Выбор ШИМ режима

| PWM11 | PWM10 | Описание |

| Работа таймера/счетчика1 в ШИМ режиме запрещена | ||

| Работа таймера/счетчика1 в 8-разрядном ШИМ режиме | ||

| Работа таймера/счетчика1 в 9-разрядном ШИМ режиме | ||

| Работа таймера/счетчика1 в 10-разрядном ШИМ режиме |

При установленном режиме широтно-импульсной модуляции таймер/счетчик 1 и регистры сравнения выхода A и B (OCR1A и OCR1B), образуют сдвоенный 8, 9 или 10- разрядный автономный генератор широтно-импульсной последовательности с выходами на выводы ОС1А и ОС1В. Таймер/счетчик1 в этом случае работает как реверсивный счетчик, считающий от $0000 до значения TOP (таблица 12.5), при котором направление счета меняется и отсчет ведется до нуля, после чего цикл повторяется.

Таблица 12.5. ТОР значения таймера и частота ШИМ

| Разрешение ШИМ | ТОР значения таймера | Частота ШИМ |

| 8-разрядное | $00FF (255) | fтс1 /510 |

| 9-разрядное | $01FF (511) | f тс1 /1022 |

| 10-разрядное | $03FF (1023) | fтc1/2046 |

Когда состояние счетчика совпадет с содержимым 10 младших битов OCR1A или OCR1B, выводы ОС1А/ОС1В устанавливаются или очищаются, в соответствии с установками битов СОМ1А1/ СОМ1А0 или СОМ1В1/СОМ1В0 в регистре управления таймером/счетчиком 1 ТСCR1А(табл. 12.6).

Таблица 12.6. Выбор функции сравнения в ШИМ режиме

| СОМ1Х1 | СОМ1Х0 | Выходной сигнал на ОСХ1 |

| Не подключен | ||

| Не подключен | ||

| Очищается по совпадению при счете вверх. Устанавливается по совпадению при счете вниз (не инвертированный ШИМ) | ||

| Очищается по совпадению при счете вниз. Устанавливается по совпадению при счете вверх (инвертированный ШИМ) |

Примечание: X = A или B.

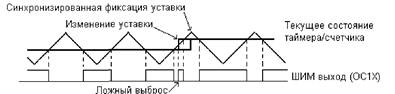

В PWM режиме младшие 10 разрядов регистра OCR1A/OCR1B, при записи, пересылаются в ячейки временного хранения. Они фиксируются по достижении таймером/счетчиком 1 значения TOP. Таким способом обеспечивается защита от появления ложных выбросов (glitches) при несинхронной записи OCR1A/OCR1B (рис. 12.5).

|

Рис. 12.5. Эффект несинхронной фиксации OCR1

При чтении OCR1A или OCR1B, в промежутке времени между записью и фиксацией, будет считано содержимое ячейки временного хранения. Это означает, что считываться из OCR1 A/B всегда будет значение записанное первым.

Когда OCR1 содержит $0 или TOP, вывод ОС1А/ОС1В остается на низком уровне, соответственно установкам СОМ1А1/СОМ1А0 или СОМ1В1/СОМ1В0. Это отображено в таблице 12.7.

Таблица 12.7. Состояния выходов в ШИМ режиме при OCR1X = $0 или TOP

| СОМ1Х1 | СОМ1Х0 | OCR1X | Состояние выводов ОС1Х |

| $0 | L | ||

| ТОР | Н | ||

| $0 | Н | ||

| ТОР | L |

Примечание: X = A или B.

В ШИМ режиме флаг переполнения таймера 1 (TOV1) устанавливается при смене направления счета по достижении значения $0. Прерывание по переполнению таймера/счетчика 1 работает так же как и в обычном режиме таймера/счетчика, т.е. оно выполняется когда флаг TOV1 (Timer Overflow Flag) в регистре TIFR установлен, установлен бит I в регистре SREG и разрешены прерывания по переполнению таймера 1.

– Конец работы –

Эта тема принадлежит разделу:

АРХИТЕКТУРА МИКРОКОНТРОЛЛЕРА

Создание фирмой Intel в году первой программируемой электронной схемы на... За лет своего бурного развития микропроцессорные системы прошли путь от специализированных комплектов интегральных...

Если Вам нужно дополнительный материал на эту тему, или Вы не нашли то, что искали, рекомендуем воспользоваться поиском по нашей базе работ: Захват, сравнение и широтно-импульсная модуляция

Что будем делать с полученным материалом:

Если этот материал оказался полезным ля Вас, Вы можете сохранить его на свою страничку в социальных сетях:

| Твитнуть |

Хотите получать на электронную почту самые свежие новости?

Новости и инфо для студентов