рефераты конспекты курсовые дипломные лекции шпоры

- Раздел Программирование

- /

- Вид работы: Лекции

- /

- Регистры состояния и управления

Реферат Курсовая Конспект

Регистры состояния и управления

Регистры состояния и управления - Лекция, раздел Программирование, Основы алгоритмизации и программирования В Процессор Включены Два Регистра, Постоянно Содержащие Информацию О Состояни...

В процессор включены два регистра, постоянно содержащие информацию о состоянии как самого процессора, так и программы, команды которой он в данный момент обрабатывает:

регистр-указатель команд EIP/IP;

регистр-указатель команд EIP/IP;

регистр флагов ЕFLAGS/FLAGS.

регистр флагов ЕFLAGS/FLAGS.

С помощью этих регистров можно также ограниченным образом управлять состоянием процессора.

Регистр-указатель команд (Instruction Pointer register) EIP/IP имеет разрядность 32(16) бита и содержит смещение следующей подлежащей выполнению команды относительно содержимого регистра сегмента кода CS в текущем сегменте команд. Этот регистр непосредственно недоступен программисту, но загрузка и изменение его значения производятся различными командами управления, к которым относятся команды условных и безусловных переходов, вызова процедур и возврата из процедур. Возникновение прерываний также приводит к модификации регистра EIP/IP.

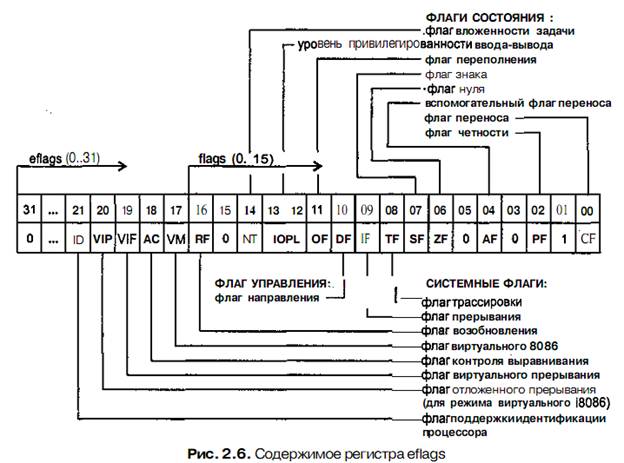

Разрядность регистра флагов (flag register) EFLAGS/FLAGS равна 32(16) битам. Отдельные биты данного регистра имеют определенное функциональное назначение и называются флагами. Младшая часть регистра EFLAGS/FLAGS полностью аналогична регистру FLAGS процессора i8086.

Исходя из особенностей использования, флаги регистра EFLAGS/FLAGS можно разделить на три группы.

В первую группу флагов регистра EFLAGS/FLAGS входят 8 флагов состояния. Эти флаги могут изменяться после выполнения машинных команд. Флаги состояния регистра EFLAGS отражают особенности результата исполнения арифметических или логических операций. Это дает возможность анализировать состояние вычислительного процесса и реагировать на него с помощью команд, условных переходов и вызовов подпрограмм.

Флаг переноса (carry flag) CF:

Флаг переноса (carry flag) CF:

1 — арифметическая операция произвела перенос из старшего бита результата, старшим является 7-й, 15-й или 31-й бит в зависимости от размерности операнда;

0 — переноса не было.

Флаг четности (parity flag) PF:

Флаг четности (parity flag) PF:

1—8 младших разрядов (этот флаг только для 8 младших разрядов операнда любого размера) результата содержат четное число единиц;

0 — 8 младших разрядов результата содержат нечетное число единиц.

Вспомогательный флаг переноса (auxiliary carry flag) AF применяется только для команд, работающих с BCD-числами. Фиксирует факт заема из младшей тетрады результата:

Вспомогательный флаг переноса (auxiliary carry flag) AF применяется только для команд, работающих с BCD-числами. Фиксирует факт заема из младшей тетрады результата:

1 — в результате операции сложения был произведен перенос из разряда 3в старший разряд или при вычитании был заем в разряд 3 младшей тетрады из значения в старшей тетраде;

0 — переносов и заемов в третий разряд (из третьего разряда) младшей тетрады результата не было.

Флаг нуля (zero flag) ZF:

Флаг нуля (zero flag) ZF:

1 — результат нулевой;

0 — результат ненулевой.

Флаг знака (sign flag) SF отражает состояние старшего бита результата (биты 7, 15 или 31 для 8-, 16- или 32-разрядных операндов соответственно):

Флаг знака (sign flag) SF отражает состояние старшего бита результата (биты 7, 15 или 31 для 8-, 16- или 32-разрядных операндов соответственно):

1 — старший бит результата равен 1;

0 — старший бит результата равен 0.

Флаг переполнения (overflow flag) OF используется для фиксации факта потери значащего бита при арифметических операциях:

Флаг переполнения (overflow flag) OF используется для фиксации факта потери значащего бита при арифметических операциях:

1 — в результате операции происходит перенос в старший знаковый бит результата или заем из старшего знакового бита результата (биты 7,15 или 31 для 8-, 16- или 32-разрядных операндов соответственно);

0 — в результате операции не происходит переноса в старший знаковый бит результата или заема из старшего знакового бита результата.

Уровень привилегированности ввода-вывода (Input/Output privilege level) IOPL используется в защищенном режиме работы процессора для контроля доступа к командам ввода-вывода в зависимости от привилегированности задачи.

Уровень привилегированности ввода-вывода (Input/Output privilege level) IOPL используется в защищенном режиме работы процессора для контроля доступа к командам ввода-вывода в зависимости от привилегированности задачи.

Флаг вложенности задачи (nested task) NT используется в защищенном режиме работы процессора для фиксации того факта, что одна задача вложена в другую.

Флаг вложенности задачи (nested task) NT используется в защищенном режиме работы процессора для фиксации того факта, что одна задача вложена в другую.

Во вторую группу флагов (группа флагов управления) регистра EFLAGS/FLAGS входит всего один флаг направления (directory flag) DF. Он находится в десятом бите регистра ЕFLAGS и используется цепочечными командами. Значение флага DF определяет направление поэлементной обработки в этих операциях: от начала строки к концу (DF = 0) либо, наоборот, от конца строки к ее началу (DF =1). Для работы с флагом DF существуют специальные команды CLD (снять флаг DF) и STD (установить флаг DF). Применение этих команд позволяет привести флаг DF в соответствие с алгоритмом и обеспечить автоматическое увеличение или уменьшение счетчиков при выполнении операций со строками.

В третью группу флагов регистра EFLAGS/FLAGS входит 8 системных флагов, управляющих вводом-выводом, маскируемыми прерываниями, отладкой, переключением между задачами и режимом виртуального процессора 8086. Прикладным программам не рекомендуется модифицировать без необходимости эти флаги, так как в большинстве случаев это ведет к прерыванию работы программы. Далее перечислены системные флаги и их назначение.

Флаг трассировки (trace flag) TF предназначен для организации пошаговой работы процессора:

Флаг трассировки (trace flag) TF предназначен для организации пошаговой работы процессора:

1 — процессор генерирует прерывание с номером 1 после выполнения каждой машинной команды (может использоваться при отладке программ,в частности отладчиками);

0 — обычная работа.

Флаг прерывания (interrupt enable flag) IF предназначен для разрешения или запрещения (маскирования) аппаратных прерываний (прерываний по входу INTR):

Флаг прерывания (interrupt enable flag) IF предназначен для разрешения или запрещения (маскирования) аппаратных прерываний (прерываний по входу INTR):

1 — аппаратные прерывания разрешены;

0 — аппаратные прерывания запрещены.

Флаг возобновления (resume flag) RF используется при обработке прерываний от регистров отладки.

Флаг возобновления (resume flag) RF используется при обработке прерываний от регистров отладки.

Флаг режима виртуального процессора 8086 (virtual 8086 mode) VM является признаком работы процессора в режиме виртуального 8086:

Флаг режима виртуального процессора 8086 (virtual 8086 mode) VM является признаком работы процессора в режиме виртуального 8086:

1 — процессор работает в режиме виртуального процессора 8086;

0 — процессор работает в реальном или защищенном режиме.

Флаг контроля выравнивания (alignment check) AC предназначен для разрешения контроля выравнивания при обращениях к памяти. Используется совместно с битом AM в системном регистре CRO. К примеру, Pentium разрешает размещать команды и данные начиная с любого адреса. Если требуется контролировать выравнивание данных и команд по адресам, кратным 2 или 4, то установка данных битов приведет к тому, что все обращения по некратным адресам будут возбуждать исключительную ситуацию.

Флаг контроля выравнивания (alignment check) AC предназначен для разрешения контроля выравнивания при обращениях к памяти. Используется совместно с битом AM в системном регистре CRO. К примеру, Pentium разрешает размещать команды и данные начиная с любого адреса. Если требуется контролировать выравнивание данных и команд по адресам, кратным 2 или 4, то установка данных битов приведет к тому, что все обращения по некратным адресам будут возбуждать исключительную ситуацию.

Флаг виртуального прерывания (virtual interrupt flag) VIF, появившийся в процессоре Pentium, при определенных условиях (одно из которых — работа процессора в v-режиме) является аналогом флага IF. Флаг VIF используется совместно с флагом VIР.

Флаг виртуального прерывания (virtual interrupt flag) VIF, появившийся в процессоре Pentium, при определенных условиях (одно из которых — работа процессора в v-режиме) является аналогом флага IF. Флаг VIF используется совместно с флагом VIР.

Флаг отложенного виртуального прерывания (virtual interrupt pending flag) VIP, появившийся в процессоре Pentium, устанавливается в 1 для индикации отложенного прерывания. Используется при работе в v-режиме совместно с флагом VIF.

Флаг отложенного виртуального прерывания (virtual interrupt pending flag) VIP, появившийся в процессоре Pentium, устанавливается в 1 для индикации отложенного прерывания. Используется при работе в v-режиме совместно с флагом VIF.

Флаг идентификации (identification flag) ID используется для того, чтобы показать факт поддержки процессором инструкции CPUID. Если программа может установить или сбросить этот флаг, это означает, что данная модель процессора поддерживает инструкцию CPUID.

Флаг идентификации (identification flag) ID используется для того, чтобы показать факт поддержки процессором инструкции CPUID. Если программа может установить или сбросить этот флаг, это означает, что данная модель процессора поддерживает инструкцию CPUID.

– Конец работы –

Эта тема принадлежит разделу:

Основы алгоритмизации и программирования

Основы алгоритмизации и программирования... Литература В И Юров Ассемблер Учебник для вузов Н И Голубь Искусство программирования на Ассемблере Лекции и упражнения...

Если Вам нужно дополнительный материал на эту тему, или Вы не нашли то, что искали, рекомендуем воспользоваться поиском по нашей базе работ: Регистры состояния и управления

Что будем делать с полученным материалом:

Если этот материал оказался полезным ля Вас, Вы можете сохранить его на свою страничку в социальных сетях:

| Твитнуть |

Хотите получать на электронную почту самые свежие новости?

Новости и инфо для студентов