Сообщения и сигналы

Сообщения и сигналы. Кодирование и квантование сигналов

Добавить а) триггер с однотактной записью (D-триггер), б) цифровой мультиплексор, в) полный одноразрядный сумматор.

Понятие о сигнале.

Однако, если ориентироваться на пособие Кнорринга (см на данном диске каталог «Пособие_метрология_....», то вот и не совсем так. Там понятие данных… Человек передает и воспринимает информацию посредством отображения ее в… Для представления данных в технических устройствах, эти данные также отображают в сигнале.Информационный параметр сигнала

При передаче голоса в телефонной системе целью является воспроизвести на приемной стороне акустические колебания для восприятия их человеческим…Аналоговый способ представления данных в сигнале.

Соответствие между исходной величиной Pзв(t) и информационным параметром U(t) может быть описано непрерывной функцией U=F(Pзв). Это соответствие… Еще одна особенность любой конкретной технической реализации устройства… Обратите внимание, что в приведенном примере входная аналоговая величина Pзв(t) непрерывно меняется в ходе течения…Представление аналоговой величины числом.

Это происходит в результате процесса измерения Сущность измерения состоит в сравнении измеряемой величины (или интенсивности проявления свойства) со… При любой технической реализации измерителя диапазон измерения оказывается… Измеренное значение выражается числом, показывающим положение значения на шкале отосительно ее начала. Поскольку…Дискретизация и квантование

В значительном количестве случаев человека интересует, как ведет себя (чаще всего, во времени) переменная величина. Даже если физик изучает… Дискретизация – это представление меняющейся величины последовательностью ее… Период повторения измерений зависит от того, насколько быстро измеряемая величина изменяется с течением времени, и для…Дискретные данные и задача их представления.

Обратите внимание, что с этих позиций можно рассматривать и результат измерения аналоговой величины (указание деления на шкале, внутри которого… Один из способов перечисления (обозначения, указания) элементов дискретных… Можно привести еще множество примеров дискретных данных: ‑ слова человеческого языка (например, русского),…Системы счисления

Функции системы счисления: - записывать количества для последующего их наглядного (зрительного) восприятия - позволять выполнять действия с… В ходе своего развития человечество изобрело весьма много различных систем… Простейшим (в смысле простоты внутренней структуры, но не в смысле простоты технической реализации устройств,…Как можно выполнить перевод из одной системы счисления в другую

Перевод из десятичной системы в двоичную можно выполнить двумя способами: 1) вычитанием степеней основания (при этом получаем последовательно… Пример: перевести 79 в двоичную систему счисления (начинаем действия справа).… Получение на очередном шаге частного =0 это признак окончания процесса. Цепочка остатков дает значение числа в…Арифметические действия над числами в позиционной системе счисления

Ограничимся правилами, справедливыми для позиционных систем счисления с постоянным основанием и с естественным порядком следования весов. Кроме… При сложении одноразрядных чисел пользуются таблицей сложения. Для десятичной… Вот как выглядит эта таблица:Алгебра логики

Это часть дискретной математики. Многозначные логики (Я. Лукасевич, 1878 – 1956) изучают функции, определенные… Бинарная логика (и соответственно бинарная, Булева алгебра – по имени ее автора английского математика Джорджа Буля,…Изображение чисел и других дискретных данных в технических устройствах

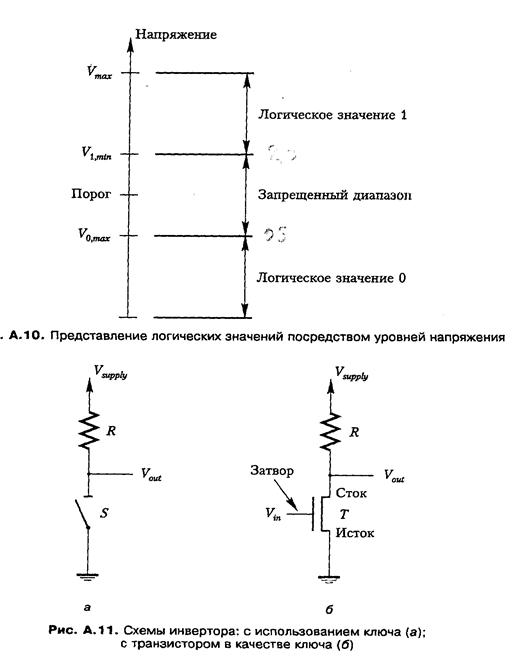

Различные цифры в техническом устройстве должны изображаться состояниями,… В данном случае речь идет об устройствах, которые способны не только изображать (хранить, передавать, отображать)…Изображение логической переменной и двоичных кодов (чисел) в электронных устройствах с использованием двухуровневого кодирования.

В некоторых узлах устройств передачи данных информационным параметром является сила электрического тока. В устройствах динамической полупроводниковой памяти, флэш-памяти… В устройствах магнитной памяти (магнитные диски) значения логической переменной изображаются величиной намагниченности…Использование логических сигналов для изображения данных

Логический сигнал можно использовать для отображения (кодирования) значения цифры одноразрядного двоичного числа. Для изображения многоразрядного… При этом возможны два различных подхода к такому изображению. При одном из них используют всего один выход (провод, контакт), на котором значения цифр двоичного числа («нули» и…Простейшие операции с аналоговыми сигналами. Операционные усилители

Преобразования аналогового сигнала на резистивной цепи.

Основные свойства операционного усилителя. Элементарные преобразования сигнала, которые осуществляет операционный усилитель.

Изменение знака аналогового сигнала.

Получение суммы и разности двух или нескольких аналоговых сигналов.

Смещение величины аналогового сигнала на постоянную величину.

Цифроаналоговые и аналогоцифровые преобразователи.

Обратное преобразование выполняют чаще всего также в два этапа: сначала цифровое значение преобразуют в электрическую аналоговую величину, а затем… Начнем рассмотрение с цифроаналогового преобразования, так как оно выполняется…Цифроаналоговые

Код 0 дает на выходе нулевое напряжение, код 1 дает на выходе Uэт. 2) Комбинация нескольких ключей, на аналоговые входы которых поданы двоично-взвешенные эталонные напряженияTERMINOLOGY ADC SPECIFICATIONS

Integral Nonlinearity

This is the maximum deviation of any code from a straight line passing through the endpoints of the ADC transfer function. The endpoints of the transfer function are zero scale, a point 1/2 LSB below the first code transition, and full scale, a point 1/2 LSB above the last code transition.

Differential Nonlinearity

This is the difference between the measured and the ideal 1 LSB change between any two adjacent codes in the ADC.

Offset Error

This is the deviation of the first code transition (0000 . . . 000) to (0000 . . . 001) from the ideal, i.e., +1/2 LSB.

Gain Error

This is the deviation of the last code transition from the ideal AIN voltage (Full Scale – 1.5 LSB) after the offset error has been adjusted out.

Signal to (Noise + Distortion) Ratio

Signal to(Noise + Distortion)=(6.02N + 1.76) dB Thus for a 12-bit converter, this is 74 dB.Total Harmonic Distortion

Total Harmonic Distortion is the ratio of the rms sum of the harmonics to the fundamental.

DAC SPECIFICATIONS

Relative Accuracy

Relative accuracy or endpoint linearity is a measure of the maximum deviation from a straight line passing through the endpoints of the DAC transfer function. It is measured after adjusting for zero error and full-scale error.

Voltage Output Settling Time

This is the amount of time it takes for the output to settle to a specified level for a full-scale input change.

Digital-to-Analog Glitch Impulse

This is the amount of charge injected into the analog output when the inputs change state. It is specified as the area of the glitch in nV sec.

--------------------------------------------------------------------------------------------------------------

Аналого-цифровое преобразование.

Для получения многоразрядного двоичного кода, значение которого функционально… Различают три классических метода аналого-цифрового преобразования. Они различаются тем, в каком порядке и с какими…Реализация логических элементов на «переключательных» схемах.

Простейшая электрическая схема, способная формировать два отчетливо различимых значения напряжения, изображающего два значения логической переменной, содержит источник питания, резистор и выключатель (ключ).

Эти схемы выполняет операцию логического инвертирования.

Первые автоматические вычислители пытались строить на электромеханических реле.

Сегодня в качестве «выключателей» в цифровых устройствах используют МОП-транзисторы.

Они бывают двух типов: n-типа и p-типа.

МОП-транзистор находится надежно в проводящем, либо в непроводящем состоянии, когда на его управляющем электроде (затворе) действует одно из двух заметно различающихся напряжений Uзакр или Uоткр.

Если управляющее напряжение затвора некотором промежуточном диапазоне, то МОП-транзистор ведет себя, как резистор, величина которого зависит от управляющего напряжения. Этот диапазон напряжений затвора инженеры-схемотехники используют для построения усилителей аналогового сигнала.

Переключательные элементы нетрудно использовать для построения простых узлов, выполняющих логические операции.

Обратите внимание, что приведенные схемы «естественным образом» выполняют логические операции ИЛИ-НЕ и И-НЕ, каждая из которых в одиночку обладает свойством функциональной полноты.

О потреблении энергии логическими элементами от источника питания.

Для устранения этого недостатка были изобретены «комплементарные» логические…О потреблении энергии, если комплементарные элементы переключаются.

и на все перезаряды в микросхеме будет расходоваться мощностьО влиянии нагрузки, подключенной к выходу КМОП элемента.

Во-первых, увеличивается величина емкости, подключенной к выходу элемента. Это приводит к увеличению потребления энергии на перезаряд суммарной… Кроме того, некоторые элементы, подключенные к выходу КМОП-каскада, могут…Двоичные логические элементы и узлы

Комбинационные логические элементы

Логический элемент – фрагмент цифрового устройства, имеющий несколько логических входов и логический выход, причем сигнал на выходе этого фрагмента… Логический элемент «И». Это фрагмент, имеющий два входа x0, x1 и один выход y,… приведено на рисунке.Используя одни простые логические функции, можно реализовать другие.

Этот пример показывает, что даже некоторые элементарные логические функции…Пример более сложной цепи: двоичный одноразрядный сумматор

Это устройство легко построить, используя ранее упомянутые логические выражения для суммы и переноса.

| Элемент «исключающее ИЛИ» формирует значение частичной суммы s (без учета переноса из младшего разряда). Элемент «коньюнктор» формирует значение переноса p (опять без учета переноса из младшего разряда) Обратите внимание, что если p=1, всегда s=0. Чтобы построить многоразрядный сумматор, надо научиться формировать сумму Sn и перенос Pn с учетом переноса Pn-1из младшего разряда: |

Полный одноразрядный двоичный сумматор также нетрудно получить.

(Добавить рисунок)

Дешифратор преобразует двоичный код в код «1 из N»

Логические узлы «с памятью»

Все логические устройства делятся на две категории: 1) комбинационные и 2) устройства с памятью (конечные автоматы или последовательностные схемы).

Комбинационные логические устройства отличаются тем, что их выходные сигналы однозначно определяются сигналами на входах устройства в данный момент времени.

Выходные сигналы схем с памятью определяются не только входными сигналами в данный момент, но и предысторией, т.е. тем, как изменялись входные (некоторые) сигналы в предшествующие моменты времени. В этом и состоит свойство памяти: наблюдая выходной сигнал устройства в данный момент, можно судить о том, как вели себя входные сигналы в прошлом.

Все рассмотренные нами до сих пор примеры логических устройств относятся к классу комбинационных.

Устройство с памятью можно построить из комбинационных элементов, если межэлементные связи образуют замкнутые контуры (например, выход элемента А подан на вход В, а выход В – на вход А).

Простейший пример устройства с обратной связью, обладающий свойством памяти, приведен на рис. Выход первого дизъюнктора соединен с входом второго, а выход второго с входом первого.

Несложно убедиться, что поведение этой цепи описывается следующей таблицей:

| Вход R | Вход S | Выход ÙQ | Выход Q | Примечание |

| 0 | 0 | Оба указанных состояния одинаково возможны (состояние хранения) | ||

| Запись «нуля» | ||||

| Запись «единицы» | ||||

| Неиспользуемая входная комбинация |

Действительно, если предположить, что при входной комбинации S=R=0 состояние выхода Q=0, то, пользуясь данными таблицы логических функций, получим состояние выхода ^Q=1 и можем убедиться, что это значение подтверждает сделанное предположение о том, что Q=0. Аналогично, если предположить, что Q=1, так же придем к тому, что ^Q=0, и что это подтверждает сделанное предположение о Q=1. При любом состоянии выходов, подача комбинации входных сигналов для записи в триггер «единицы» ‑ S=1, R=0, приводит к состоянию Q=1, ^Q=0 и т.д.

(Перерисовать RS-триггер симметрично)

(Нарисовать тактируемый RS-триггер)

(Нарисовать триггер с однотактной записью ‑ D-триггер)

(И, наконец, D-триггер, тактируемый фронтом синхросигнала)

(Показать, как этот D-триггер можно превратить в разряд счетчика)

(Показать, как для всех типов D-триггеров можно добавить входы раздельной установки.

Регистр – логическая схема с памятью, предназначенная для запоминания многоразрядного двоичного слова. В состав регистра входит несколько триггеров, количество которых равно числу разрядов в запоминаемом двоичном слове. Функционирование регистра можно представить следующей моделью:

| при кратковременном действии на входе разрешения записи C активного фрагмента сигнала регистр запоминает в своих триггерах состояния входов D0,D1,… и в дальнейшем удерживает запомненные значения на выходах Q0,Q1,…. Иногда регистры имеют более сложное внутреннее устройство, и способны выполнять добавочные функции над записанным двоичным словом, в частности его сдвиг. |

Счетчик – разновидность регистра, который способен изменять на единицу записанное двоичное число при действии активного фрагмента сигнала на счетном входе T.

| Обычно счетчик, подобно простому регистру, имеет входы D и Cдля (параллельной) записи в него исходного содержимого. Различают а) суммирующие счетчики (при действии на входе Tсодержимое (интерпретируемое как двоичное число) увеличивается на 1, б) вычитающие (число уменьшается на 1) и реверсивные (направление счета можно выбирать). При достижении максимального числа (все 1 в двоичном содержимом) происходит «переполнение» счетчика (wrap-around) – содержимое становится «нулевым», при этом появляется сигнал на выходе переполнения OV. |

Счетчик можно использовать как преобразователь последовательного унарного кода в позиционный двоичный код.