рефераты конспекты курсовые дипломные лекции шпоры

- Раздел Образование

- /

- Задача №1

Реферат Курсовая Конспект

Задача №1

Задача №1 - раздел Образование, Задача №1 ...

Задача №1

Uвх =Ni (V), fвх = Ni (kHz), Cк =Ni x 0,01 (mkF), R1 = R2 = 10-kOm, где Ni– порядковый номер студента в журнале группы.R1 = R2 = 10 kOm

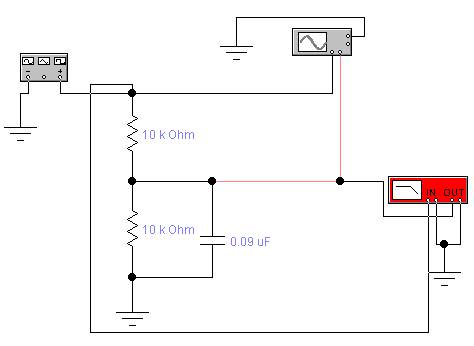

Частотно-компенсированный делитель напряжения представляет из себя такую схему:

Емкость компенсирующего конденсатора можно определить как равным конденсатору Ск, так как величины обеих сопротивлений в делителе тоже равны. Равенство конденсаторов и резисторов обеспечит одинаковые постоянные времени обеих цепей.

Амплитуда выходного сигнала будет равна половине амплитуде входного, так как делитель является частотно-скомпенсированным и значение имеет только соотношение величин сопротивлений, а поскольку они равны, то и сигнал делится пополам.

Без конденсатора Ск такая цепь превращается в фильтр низших частот. Его схема:

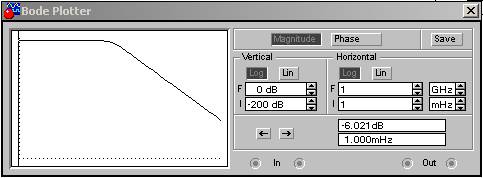

Частотная характеристика такой цепи представлена на рисунке:

На нем видено как увеличивается коэффициент деления с ростом частоты. Это связано с тем, что реактивное сопротивления конденсатора для более высоких частот меньше чем для низких.

Значение граничной частоты fгру делителя без Ск равно 125 Гц.

Fгр =1/R*C

Fгр=1/0.009=111,11

У частотно-скомпенсированного делителя граничной частоты в идеальном случае нет.Uогр2 = -- 14

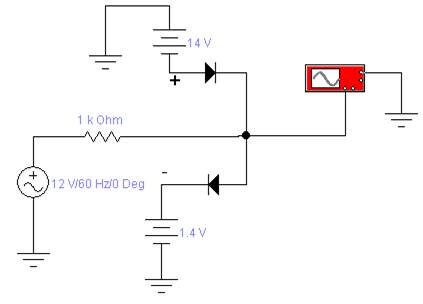

Двухсторонний параллельный диодный ограничитель представлен на схеме:

Его работа основана на свойстве диода проводить ток только в одном направлении. Когда напряжение сигнала превышает величину напряжения приложенного с обратной стороны диода, он открывается и шунтирует сигнал.

Форма сигнала после диодного ограничителя показа на рисунке:

Положительная полуволна ограничивается на уровне 2,12 В которое складывается из Uогр1и величины падения напряжения на диоде (0,7 В.). Отрицательная полуволна не ограничивается так как величина приложенного напряжения равного 14 В, больше амплитуды сигнала.

Форма сигналов на выходе при использовании в схеме такого ограничителя идеальных и реальных диодов будет отличатся тем, что у идеальных диодов нет падения напряжения в прямом включении. Ограничение сигнала при использовании идеальных диодов будет по уровню 1,4 В в положительной полуволне.

Если в схеме такого ограничителя вместо обычных диодов VD1 иVD2 будут использоваться стабилитроны (например, КС133А с напряжением стабилизации примерно равным 3 В) форма сигнала на выходе станет такой:

Схема подключения стабилитронов:

Задача № 7.

Предложите 2-х входовый аналоговый инвеpтиpующий сумматор (SM) на основе операционного усилителя (ОУ).

В ответе привести: функциональную схему SM с идеальным ОУ; краткое описание работы; расчеты входных pезистоpов и напряжения на выходе (Uвых) при условиях:

К1=0,5

К2=4

U1=4 В,

U2=3 В,

Rос=30 кОм,

где Кi – коэфициент передачи сигнала с i-го ( i=1,2) входа,

Rос - резистор обpатной связи,

Ui- входные сигналы постоянного тока ;

форму Uвых при условии, что на второй вход поданы 2-х полярные синусоидальные сигналы U2 с амплитудой 5 В при питании ОУ = ± 6В.

Решение

Поскольку : Iвх = Uвх / R1 ; Iос = - Uвых / R2 ,Решение

На входе и выходе формирователя присутствуют такие сигналы:Решение

Рассчитаем номиналы цепей обратных связей. Для неинвертирующего усилителя коэффициент усиления находим по формуле: К=1+Roc/R отсюда R= Roc/(К-1)– Конец работы –

Используемые теги: Задача0.039

Если Вам нужно дополнительный материал на эту тему, или Вы не нашли то, что искали, рекомендуем воспользоваться поиском по нашей базе работ: Задача №1

Что будем делать с полученным материалом:

Если этот материал оказался полезным для Вас, Вы можете сохранить его на свою страничку в социальных сетях:

| Твитнуть |

Хотите получать на электронную почту самые свежие новости?

Новости и инфо для студентов